JPEG解碼器IP核的設計與實現

1.6 IDCT模塊設計

2D-IDCT的實現選用行列分解法,所以主要功能模塊包括1D-IDCT模塊和行列轉置模塊。因為全流水線實現系統解碼硬件成本很高,所以設計中主要通過提高運算并行度和在功能模塊內部實現流水線運算來提高解碼速度。IDCT模塊設計中采用了兩個1D-IDCT處理單元,并通過流水線技術實現高運算速率。

1.6.1 1D-IDCT模塊設計

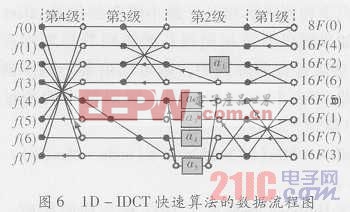

本設計采用了一種運算量少、數據流簡單且適于流水線實現的IDCT算法。通過對1D-IDCT數據流程的合理劃分,將其分4級,在每級中間插入寄存器,對每級流水線內部運算的時序進行合理安排,在每級流水線內共享算術單元,降低硬件成本。1D-IDCT快速算法的數據流程如圖6所示。

本文引用地址:http://www.104case.com/article/162053.htm

本文引用地址:http://www.104case.com/article/162053.htm

通過對1D-IDCT數據流程的合理安排和資源共享,本設計共需4個加法器,4個減法器和4個乘法器,所用硬件資源比較少。而且本設計的處理速度快,每個時鐘周期輸入兩個像素,完成1D-IDCT的延遲時間是6個時鐘周期。在流水運算時計算一個8點1D-IDCT只需要4個時鐘周期。

1.6.2 行列轉置模塊設計

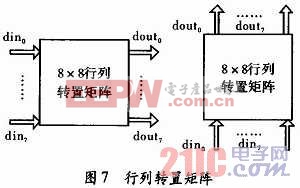

行列轉置矩陣的實現大部分設計采用雙RAM進行乒乓操作完成,本設計采用一個8×8寄存器陣列和方向控制信號完成,可節省一半硬件資源,且控制簡單。當有信號輸入時,方向控制信號值初始設為0,這時寄存器陣列的輸入輸出方向是從左到右,64個時鐘周期后方向控制信號反向變為1,這時寄存器陣列的輸入輸出方向是從下到上。如此循環,即可實現行列轉置,如圖7所示。

2 綜合、仿真與性能分析

設計時先用Matlab進行算法級仿真與驗證,在RLT級設計時采用Verilog語言實現,在Modelsim6.1中進行功能仿真,選擇VIRTEX2系列xc2v250器件進行FPGA驗證,從軟硬件方面都驗證了設計的正確性。

使用Synopsys公司的Design Compiler工具在0.18μm的SMIC CMOS工藝條件下,對RTL代碼進行綜合優化。通過設置不同的面積、時序及功耗約束條件,縮短關鍵路徑的延時,時鐘頻率可達100 MHz的最優設計,綜合出面積為721 695μm2,不包括存儲單元需要34.6 kB標準門。本設計能每秒能夠解碼1 920×1 080圖形25幀以上,所以也能用于一些有低成本需求的監控、錄像系統。

3 結束語

介紹了基于靜止圖像壓縮標準JPEG的解碼器IP核的設計,描述了硬件設計過程,提出了一種高效、低成本的JPEG解碼器架構。設計通過VIRTEX2平臺進行了FPGA驗證,并使用Synopsys公司的DC工具在SMIC 0.18 μmCMOS工藝條件下,對設計進行面積和時間的優化,在100 MHz時鐘頻率下工作時電路面積為721 695μm2,每秒能夠解碼1 920×1 080圖形25幀以上。本設計還支持多種圖像質量和圖像格式,有較寬的壓縮比范圍,設計具有獨立性和完整性,也適用于數碼相機、手機和掃描儀等各種應用。

評論