基于Nios II軟核的內河航標監控系統設計

1.1 外圍設備

外圍設備是指某些具體控制電路或模塊接口,它們都是非邏輯的,而且無法在FPGA/CPLD中用可編程邏輯來實現。

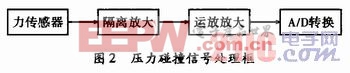

1.1.1 碰撞壓力處理電路

對航標是否受到碰撞須作實時監控,避免航標受碰撞損壞,而導致未能給航行體作正確指示,根據系統設計要求,碰撞壓力信號測量的電路設計如圖2所示。本文引用地址:http://www.104case.com/article/161441.htm

力傳感器采樣數據送兩級運放LM324進行調節放大后,送入雙12位A/D轉換器的VA1和VA2。AD7862以250 kHz的采樣率同時進行4個通道信號采樣,輸入給片內采樣一保持放大器的信號經差分并在ADC輸入期間內保持,將模擬信號轉換成系統需要的數字信號。

1.1.2 GSM、GPS模塊

控制中心GSM Modem選用Siemens公司的無線通信引擎TC35終端,它由引擎模塊、天線及其外圍電路組成。監控終端TC35i模塊的用戶口采用40腳的ZIP插座,其中包含了模擬音頻、RS232接口、SIM卡接口和電源,外圍電路主要是SIM卡電路和啟動控制電路。

GPS數據采集模塊采用美國泰雷茲導航定位公司(Thales Navigation)的一款高性能、低功耗的小型GPS接收機B12 OEM,通過獨特的軟件算法和最新的GPS技術,泰勒茲公司把B12優化成快速處理、導航、車輛跟蹤、移動數據、遠程信息處理的手持產品。它支持差分遠程操作,可提高系統差分定位精度。

1.2 片內邏輯的設計

將概念結構轉化為與實際系統相應的數據模型的過程稱為邏輯結構設計。FPGA的片內邏輯設計,包括系統模塊和用戶自定制邏輯區域。系統模塊是指由SOPC builder自動生成的設計,SOPC builder會根據用戶選擇的IP生成相應的HDL描述文件。用戶自定制邏輯區域內可以包含用戶自定義的Avalon外設,以及與系統模塊無關的其他用戶自定制邏輯。

利用FPGA中的可編程邏輯資源和現有IP軟核,如Nios II核、片內Boot ROM、用于FIFO的片內雙口RAM、定時器Timer、JTAG UART等來構成該嵌入式系統處理器的接口功能模塊。

1.2.1 串行通信接口UART

UART是基于RS232通信協議的串行通信接口,用于在Altera的FPGA中實現簡單的RS232異步發送和接收邏輯。因為GSM、GPS模塊兩者的數據通信接口都為標準RS232串行接口,因此,可方便地與NiosⅡ系統的串口相連。

圖1所示的監控終端硬件設計框圖中,UART-1連接GSM短消息發送模塊TC35i,利用AT命令控制TC35i收發信息和撥號,控制中通過RS232串口與GSM TC35 Modem通信。GSM模塊接入GSM網絡,按照規定的通信協議,以短信方式完成航標的工作參數與狀態信息的傳輸。

UART-2連接GPS OEM板,通過GPS定位模塊的接收天線接收導航信號,經接收機解調處理,獲取航標燈的位置信息,包括航標燈的代碼、位置的經緯度、測定時間等信息,再將經緯度坐標通過無線通訊系統傳送給監控中心。

評論