基于EPM1240的SDRAM控制器的設計

2.3 突發長度模塊

突發長度也使在模式寄存器中設置的,它的內部實質是4位遞增計數器,這一計數器監視讀寫突發工作時的時鐘周期數,原理與2位遞增計數器相同。

突發長度可以是1、2、4或者8,突發(Burst)是指在同一行中相鄰的存儲單元連續進行數據傳輸的方式,連續傳輸所涉及到存儲單元(列)的數量就是突發長度。

2.4 地址轉換模塊

地址發生器將微處理器提供的地址按照要求的格式映射到移動SDRAM設備上。命令模塊接收控制接口模塊輸入的解碼后的命令和刷新控制單元發出的刷新請求命令,產生合適的SDRAM操作命令。

該模塊包含一個簡單的仲裁邏輯單元,仲裁主接口和刷新單元發出的命令,刷新請求的優先級最高。當刷新單元和主接口同時發出命令時,仲裁單元掛起主接口的命令直到刷新操作執行完畢;若主接口發出的命令正在執行時,仲裁單元掛起刷新命令直至正在處理的操作執行結束。仲裁單元接收控制接口模塊發出的命令后,命令產生單元根據接收到的命令產生合適的SDRAM控制信號。命令產生單元基于三個移位寄存器產生正確的時序:第一個寄存器控制SDRAM激活命令的時序;第二個寄存器控制SDRAM讀寫時的時序;第3個用于產生命令延時,以便決定所請求的命令是否執行完畢。它根據狀態分別產生塊和行列地址,并傳送到移動SDRAM設備上。

地址發生器的輸入輸出如下:

clk是系統的主時鐘輸入,addr是輸入的地址信號,pr_state是輸入的當前狀態,這3個信號均由微控制器提供。地址發生器接收來自微控制器的命令,把命令轉換成SDRAM能夠理解的狀態信號,地址發生器根據狀態信號產生相應的地址選擇SDRAM的行或列進行操作。

3 系統的設計與實現

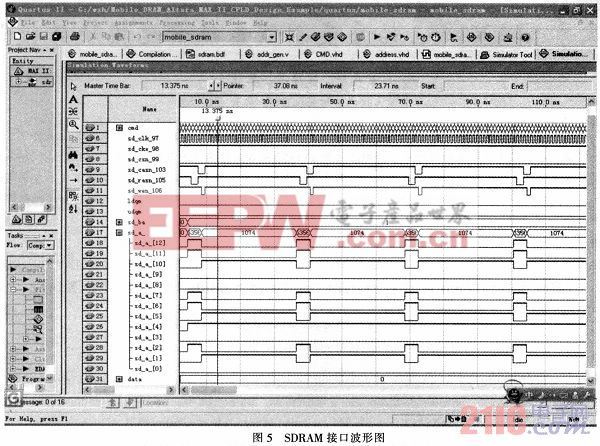

選擇ALTERA公司MAXⅡ系列的EPM1240芯片,用CPLD方式實現SDRAM接口。接口仿真時序圖如圖5所示。本文引用地址:http://www.104case.com/article/161059.htm

SDRAM接口仿真波形圖如圖5所示,其中sd_clk_97為操作SDRAM的時鐘,sd_cke_98,sd_csn_99,sd_casn_103,sd_rasn_105,sd_wen_106分別為時鐘使能信號,片選信號,列選通信號,行選通信號和讀寫使能信號。sd_ba是SDRAM的2位Bank地址線,sd_a_是SDRAM的13根地址線。data為SDRAM的16位輸入/輸出雙向數據線。

4 結論

在SDRAM的接口設計中,刷新的實現一直是一個關鍵問題。選用CPLD產生控制SDRAM的時序,實現對SDRAM的各種操作。應用Verilog語言和QuartusⅡ軟件實現了SDRAM的接口設計,在QuartusⅡ軟件環境下模擬了STM32系列單片機對SDRAM的讀寫操作時序,讀寫速度達到100MHz,可以在STM32系列單片機擴展64 MBit的SDRAM,其中SDRAM的地址線為13根(行地址線13根,列地址線9根),Bank地址線2根,數據線16根。

評論