基于EPM1240的SDRAM控制器的設計

1.2 預充電

由于SDRAM的尋址具有獨占性,所以在進行完讀寫操作后,如果要對同一L-Bank的另一行進行尋址,就要將原來有效(工作)的行關閉,重新發送行/列地址。L-Bank關閉現有工作行,準備打開新行的操作就是預充電(Precharge)。預充電可以通過命令控制,也可以通過輔助設定讓芯片在每次讀寫操作之后自動進行預充電。實際上,預充電是一種對工作行中所有存儲體進行數據重寫,并對行地址進行復位,同時釋放S-AMP(重新加入比較電壓,一般是電容電壓的1/2,以幫助判斷讀取數據的邏輯電平,因為S-AMP是通過一個參考電壓與存儲體位線電壓的比較來判斷邏輯值的),以準備新行的工作。具體而言,就是將S-AMP中的數據回寫,即使是沒有工作過的存儲體也會因行選通而使存儲電容受到干擾,所以也需要S-AMP進行讀后重寫。此時,電容的電量(或者說其產生的電壓)將是判斷邏輯狀態的依據(讀取時也需要),為此要設定一個臨界值,一般為電容電量的1/2,超過它的為邏輯1,進行重寫,否則為邏輯0,不進行重寫(等于放電)。為此,現在基本都將電容的另一端接入一個指定的電壓(即1/2電容電壓),而不是接地,以幫助重寫時的比較與判斷。

1.3 刷新

SDRAM之所以稱為同步動態隨機存儲器,就是因為它要不斷進行刷新(Refresh)才能保留住數據,因此它是SDRAM最重要的操作。刷新操作與預充電中重寫的操作一樣,都是用S-AMP先讀再寫。進行預充電操作還要進行刷新的原因:因為預充電是對一個或所有L-Bank中的工作行操作,并且是不定期的,而刷新則是有固定的周期,依次對所有行進行操作,以保留那些久久沒經歷重寫的存儲體中的數據。但與所有L-Bank預充電不同的是,這里的行是指所有L-Bank中地址相同的行,而預充電中各L-Bank中的工作行地址并不是一定是相同的。

目前公認的標準是,存儲體中電容的數據有效保存期上限是64 ms,也就是說每一行刷新的循環周期是64 ms,這樣刷新速度就是:行數量/64 ms。內存規格有4096Refresh Cyeles/64 ms或8192 Refresh Cycles/64 ms的標識,這里的4096與8192就代表這個芯片中每個L-Bank的行數。刷新命令一次對一行有效,發送間隔也是隨總行數而變化,4096行時為0.625 ps,8192行時就為7.812 5 ps。刷新操作分為兩種:自動刷新(Auto Refresh,簡稱AR)與自刷新(Self Refresh,簡稱SR)。不論是何種刷新方式,都不需要外部提供行地址信息,因為這是一個內部的自動操作。

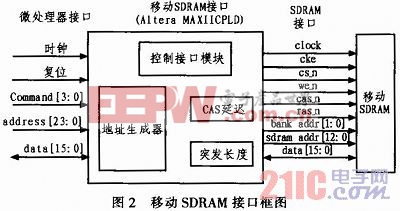

2 系統硬件設計

移動SDRAM接口設計包括四個主要模塊,如圖2所示,即控制接口模塊、CAS延遲、突發長度以及地址生成器。下面對這些模塊進行簡要介紹。本文引用地址:http://www.104case.com/article/161059.htm

2.1 控制接口模塊

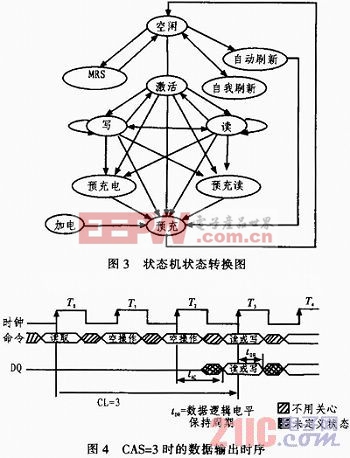

控制接口模塊內部是有限狀態機(Finite-State Machine,FSM),有限狀態機解釋來自微處理器的輸入,把相應的命令和符合時序要求的地址發送給移動SDRAM設備,然后,移動SDRAM設備進入相應的狀態,執行命令。

有限狀態機會綜合考慮存儲器的時序要求,以正確的順序產生各種操作指令,在發出操作指令之前,控制器首先會給出一個讀取使能信號,從數據輸入輸出緩存模塊的地址指令中讀取地址指令。控制接口模塊解碼并寄存主機發送的命令,把解碼后的空閑、寫、讀、刷新、充電和模式設置命令和地址信號送給命令模塊。狀態機的狀態轉換如圖3所示。

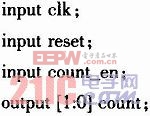

2.2 CAS延遲模塊

CAS延遲通過模式寄存器配置,CAS延遲模塊的實質是2位遞增計數器,這一計數器監視CAS延時時鐘周期數。它表示讀命令和第一個輸出數據之間延遲的時鐘周期數,延時時鐘周期數可以是二或三個時鐘周期。圖4分別給出CAS=3時的數據輸出時序。

2位遞增計數器的輸入輸出如下:

clk是輸入的時鐘信號來自微控制器,reset輸入的異步復位信號,count_en輸入的計數使能信號,count輸出的CAS延遲數。系統不復位的情況下在計數使能有效時當時鐘上升沿到來CAS延遲增加。

評論