基于DDS的高速定時同步方法

2 直接數字頻率合成

直接數字頻率合成(DDS)用于實現鎖相環的VCO。DDS的原理如圖2所示。本文引用地址:http://www.104case.com/article/160293.htm

DDS由相位累加器、正弦表、DAC和濾波器組成。相位累加器長度為N位,顯然2N相當于360°(2π rad)。DDS是以系統時鐘頻率fs對相位進行等間隔的采樣,每個系統時鐘周期Ts輸出頻率fo的相位增量為FW×2π/2N。完成一整周正弦輸出需要2π/(FW×2π/2N),即2N/FW個系統時鐘周期,可以得到輸出頻率:

![]()

由式(5)可知,相位累加器的長度N越大,DDS的頻率分辨率越高。如果將相位累加器全部字長作為正弦表的地址將會占用很大的存儲空間,一般只選取最高的W位。這樣既獲得了高的頻率分辨,又節省了存儲空間。正弦表的輸出經DAC變為模擬信號,再由濾波器濾除DAC采樣時鐘的諧波得到期望的輸出頻率fo。

目前DDS技術已經比較成熟,已有很多DDS芯片可供選持。AD9912是AnaLog Devices的高性能DDS器件,其系統時鐘高達1 GHz,相位累加器高達48位。由式(5)可知其頻率分辨優于4μHz,足夠滿足一般通信系統定時同步的要求。

3 基于DDS的定時同步方法

高速數據傳輸的數據速率為300 Mb/s,調制體制采用QPSK。QPSK兼顧了頻率效率和帶寬效率,是高速數據傳輸中應用最廣泛的調制體制。鎖相環的鑒相器采用Gardner算法。Gardher算法提取時鐘誤差獨立于載波相位,即定時同步時不需先進行載波同步。Gardner算法每個符號只需兩個采樣點,即只要求采樣速率是符號速率的兩倍。QPSK的Gardner定時誤差表達式為:

![]()

式中:y1(r),yQ(r)表示I,Q兩路第r個符號判決時刻樣點值;y1(r-1/2),yQ(r-1/2)表示介于第r個符號和第r-1個符號中間的樣點值。

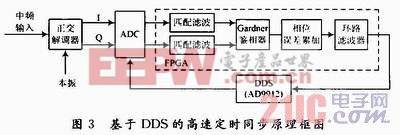

基于DDS的高速定時同步原理框圖如圖3所示。

中頻輸入與本振在正交解調器內混頻解出QPSK的I,Q兩條支路信號。QPSK每條支路的數據速率為其總速率的1/2,故I,Q的速率為150 Mb/s。ADC對I,Q兩路分別采樣,采樣時鐘頻率為300MHz(支路數據速率的2倍),采樣時鐘由DDS產生。ADC采樣后的信號送到FPGA進行處理,FPGA選為Xilinx公司Virtex-5系列中的XC5VSX95T,其內部豐富的DSP資源適合算法實現。在FPGA內,I,Q采樣信號首先進行平方根升余弦匹配濾波,然后送到Gardner鑒相器提取相位誤差。相位誤差累加后以較低的100kHz速率送給環路濾波器進行更新。選ζ=0.707,ωn=100Hz,由式(4)可汁算出環路濾波器的參數C1和C2。環路濾波器輸出的頻率控制字送到DDS調整其輸出采樣時鐘相位完成定時同步環路的閉環控制。

4 結論

定時同步是高速數據傳輸的一項關鍵技術。在對鎖相環和DDS原理分析的基礎上提出了基于DDS的高速定時同步方法,采用該方法設計了300Mb/s解調器進行實驗測試,取得了滿意的結果。基于DDS的高速定時同步方法也適用于更高速率的數據解調,為高速數據傳輸方案設計提供了參考。

評論