一種基于FPGA的DDR SDRAM控制器的設計

3 DDR SDRAM控制的仿真和驗證

3.1 DDR SDPAM控制器的軟件仿真

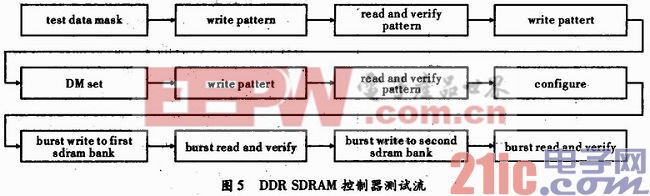

設計的軟件功能仿真是利用硬件描述語言VerilogHDL寫出測試代碼,在Mentor公司的Modelsim軟件中進行,通過檢查波形完成。DDR SD RAM控制器測試流如圖5所示,實現了寫數據到第1組寄存器,讀校驗數據,寫數據到第2組寄存器,讀校驗數據。本文引用地址:http://www.104case.com/article/159415.htm

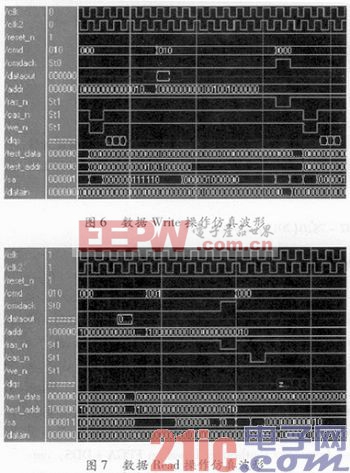

當控制器接收到請求發送數據的命令后,由命令引腳產生相應的Write命令傳送給DDR SDRAM,接下來會反饋—個握手信號ready以告知用戶端已準備就緒可以繼續接收數據,而接收到的數據通過dq端口直接傳給DDR SDRAK。經過Modelsim功能仿真Read/Write波形如圖6和圖7所示,結果表明DDR SDRAM能順利地完成讀寫、刷新和預充電,行與行、塊與塊之間的交換平穩迅速,無論是連續還是單個操作都非常順暢。

3.2 DDR SDRAM控制器的FPGA驗證

設計的DDR SDRAM控制器硬件驗證在Altera公司CycloneII系列的EP2C5Q208C8 FPGA芯片中進行,利用在線仿真技術快速建立芯片設計的硬件模型,然后將設計映射至目標FPGA電路中,通過加載設定的激勵信號,觀察所輸出的結果并與所期望的輸出結果進行比較,發現寫入和輸出的數據完全吻合。經過綜合,基礎邏輯單元資源占用率為12.33%,引腳資源占用率為62.5%,鎖相環PLL資源的占有率為50%,流片頻率測試也能達到期望要求,能完全勝任對DDRSDRAM控制。

4 結束語

在研究DDR SDRAM的主要工作特性以及時序的基礎上,利用Verilog HDL硬件描述語言提出了一種適用于DDR SDRAM的控制器的設計。并且通過了Modelsim軟件功能仿真、FPGA硬件驗證,結果表明該設計傳輸數據穩定可靠,讀寫效率較高,接口電路簡單,可應用于各種高速度、大容量存儲器場合中。

電容器相關文章:電容器原理

fpga相關文章:fpga是什么

電荷放大器相關文章:電荷放大器原理 漏電開關相關文章:漏電開關原理 鎖相環相關文章:鎖相環原理

評論