U盤SoC的設計與實現

摘要:設計和實現了U盤SoC。本系統包括USB CORE和已驗證過的CPU核、Nandflash、UDC_Control等模塊,模塊間通過總線進行通信。其中USB CORE為本文設計的重點,用Verilog HDL語言實現,同時并為此設計搭建了功能完備的Modelsim仿真環境,進行了仿真驗證。

關鍵詞:U盤;片上系統;USB;Verilog HDL

隨著便攜式設備的廣泛使用,移動存儲設備被廣泛用于信息存儲和傳輸。在目前諸多存儲設備中,U盤憑借其體積小、容量大、攜帶方便、支持熱插拔等諸多優點,得到了迅速的普及。而且隨著USB技術的廣泛應用,在各種SoC系統中集成USB功能也成為一種必然趨勢。所以對SoC芯片中集成USB接口的研究開發,具有較高的實用價值。

文中通過分析USB協議,設計出了一種符合該協議的低速和全速的USB設備控制器,并將該控制器與8051CPU核,NandFlash,UDC_Control通過總線連接起來,組成了一個U盤SoC系統,并對此U盤SoC系統加以仿真驗證。

1 系統的整體設計

現在的USB控制器主要有兩種:帶USB接口的單片機(MCU)和純粹的USB接口芯片。純粹的USB接口芯片僅處理USB通信,必須有一個外部微處理器來進行協議處理和數據交換。帶USB接口的單片機從應用上又可以分成兩類,一類是從底層設計專用于USB控制的單片機;另一類是增加了USB接口的普通單片機,這類USB控制器的最大好處在于開發者對系統結構和指令集非常熟悉,開發工具簡單,但價格比較高,不利于產品升級和改型。

根據上述情況,文中介紹了一種U盤SoC設計:將CPU和USB CORE通過UDC_Control模塊連接起來,再加上NandFlash模塊,通過總線連接組成一個SoC系統。其整體框圖如下圖1所示。

2 模塊的詳細設計

2.1 USB CORE

此模塊為該設計的核心模塊,實現USB1.1總線接口層設備控制器的功能,是本文設計的重點。USB設備控制器的架構框圖如圖2所示,rxdp、rxdm為從主機發送過來的信號,txdp、txdm為USB模塊發送給主機的信號。其中MCU通過控制SIE來對USB設備進行控制。如圖2所示,本設計分為6個模塊。下面分別介紹各個模塊。

2.1.1 rx模塊

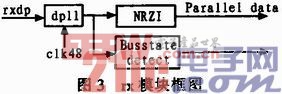

rx模塊是總線接收模塊,實現USB數據傳輸接收物理層的功能,把串行的USB數據去掉數據包頭,進行NRZI解碼,去掉填充位,并將串行的數據轉換成并行的8位數據。然后將數據送往下一模塊處理。本模塊又分為dpll、解碼和總線狀態監測模塊。如圖3所示。

dpll模塊用48 MHz的時鐘把總線上傳輸的時鐘和數據信號恢復出來。用48 MHz的時鐘對總線上的數據信號進行采樣,以去掉抖動,然后產生總線信號電平變化的指示信號change信號,change信號的改變可控制采樣點,從而保證數據信號的采樣點固定在每位數據信號的中央。

NRZI解碼模塊檢測到同步頭后,根據NRZI的原理,將rxdp和rxdp延后一拍的數據進行同或操作,得到的數據經過去填充位,串并轉換后,送入解包模塊。

總線狀態監測模塊監測總線的狀態,置位suspend,resume,reset等狀態指示信號。若Idle時間超過3ms時,就將suspend信號置高,在suspend狀態時檢測到總線信號變化時,將resume信號置高,若se0時間超過2.5μs時,就將reset信號置高。

2.1.2 解包模塊

本模塊接收從rx模塊送過來的并行數據,按照USB數據包協議規范對接收的數據進行解釋,并對數據做CRC校驗,給出當前接收包的類型,根據不同類型的包的結構,從包中解出相應的信息送給下一模塊。

2.1.3 req_dec模塊

本模塊對setup階段USB的標準請求進行解釋,提供和USB請求相關的信號給SIE模塊,判斷funetion和endpoint的地址是否合法。若標準請求中對某個端點所請求的操作和預定的不符,則會產生錯誤信號。

2.1.4 SIE模塊

SIE(Serial Interface Engine)模塊是USB CORE的核心模塊,根據從解包模塊傳送過來的信號與從MCU傳送過來的接口握手信號,按照USB的相關協議,產生打包模塊的控制信號和MCU的控制信號,從而控制總線上的數據發送。

評論