集成CMOS對稱式收/發(fā)開關(guān)的設(shè)計

TD-SCDMA使用的是時分雙工方式(TDD)。對于TDD通信系統(tǒng)來說,高質(zhì)量的收/發(fā)開關(guān)是RF前端電路的關(guān)鍵模塊。為了提高集成度,收/發(fā)開關(guān)可以采用全集成的形式來取代傳統(tǒng)的GaAs MOSFET和PIN二極管等分立元件。

使用CMOS收/發(fā)開關(guān)取代GaAs MOSFET收/發(fā)開關(guān)的好處之一是CMOS開關(guān)電路不需要負的控制電壓。而且,如果能用標準CMOS工藝來完成,開關(guān)電路就可以和收發(fā)器中其它RF模塊集成在一起,這將降低成本。

TD-SCDMA系統(tǒng)規(guī)劃使用的頻段主要為1900MHz-1920MHz和2010MHz-2025MHz。本文采用TSMC 0.35m CMOS工藝來制作射頻收/發(fā)開關(guān)。通過優(yōu)化設(shè)計,該開關(guān)電路在2GHz處取得了較好的仿真結(jié)果。

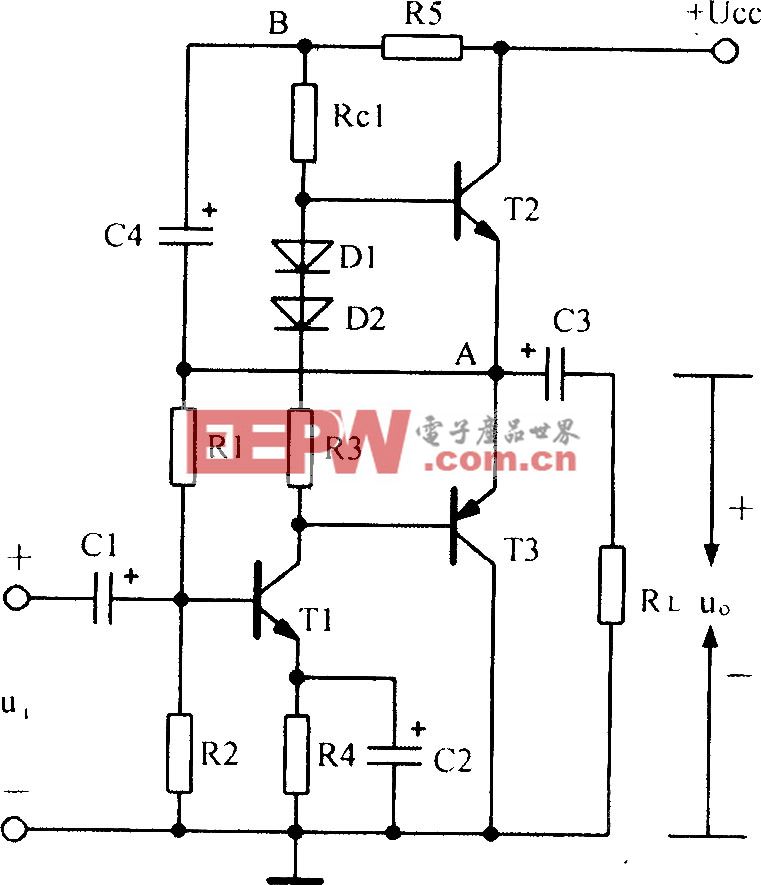

圖1 對稱式收/發(fā)開關(guān)電路示意圖

圖2 MOSFET導通時的等效電路圖

圖3 開關(guān)截止一側(cè)的小信號等效電路

(a) 插入損耗

(b) 隔離度

優(yōu)化設(shè)計

圖1是對稱式串并結(jié)構(gòu)NMOS射頻開關(guān)的電路示意圖。串聯(lián)的晶體管M1和M2完成主要的開關(guān)功能。并聯(lián)的晶體管M3和M4通過將截止晶體管一側(cè)的射頻信號導通到地來提高開關(guān)電路的隔離度。控制電壓Vctrl 和用于控制晶體管M1和M2的開與合。當Vctrl為高電平時,M1導通,M2截止,開關(guān)處于發(fā)射狀態(tài);當為高電平時,M1截止,M2導通,開關(guān)處于接收狀態(tài)。該開關(guān)電路還包括旁通電容C1和C2,它們提供了開關(guān)電路中TX和RX端口的直流偏置。MOS管柵極上的偏置電阻R1、R2、R3和R4的作用是提高隔離度和線性度。本設(shè)計中,串聯(lián)MOS管柵寬取200m,并聯(lián)MOS管的柵寬取100m,旁通電容C1和C2取5pF,柵極偏置電阻R1、R2、 R3和R4均取10K。

射頻收/發(fā)開關(guān)的重要性能指標為:插入損耗(IL)、隔離度(Isolation)和線性度(通常用1dB壓縮點P1dB來表示)。其中插入損耗是設(shè)計的重點。

插入損耗

插入損耗表示當開關(guān)導通時射頻信號通過射頻開關(guān)的功耗。

管子的導通電阻是影響插入損耗的關(guān)鍵因素之一。因此,在本設(shè)計中只使用nMOSFET。由于硅襯底的導電特性,管子的漏極和源極對襯底的結(jié)電容及相關(guān)的寄生電容也是影響插入損耗的主要因素。

為了簡化,只分析包含單個MOS管的電路,圖2為其導通時的等效電路圖。在這個分析中,假設(shè)管子偏置在線性區(qū)。圖2中,Vrf、Rs分別為等效信號源及源內(nèi)阻,Ron為MOS管的導通電阻,Rb為其襯底電阻,Rl為負載電阻,Ct是其等效電容(虛線部分),其等效式為:

如果負載端和源端都與特征阻抗(Z0)匹配,則插入損耗可以用正向傳輸系數(shù)的幅度平方(|S21|2)的倒數(shù)來表示。

由該表達式可以看出,導通電阻Ron越大,插入損耗越大;寄生耦合電容Ct越大,插入損耗越小;襯底電阻對插入損耗的影響并不呈簡單的線性關(guān)系。實際上,有一個使插入損耗最大的襯底電阻Rb(max)

因此,用CMOS技術(shù)制作的RF開關(guān)電路要獲得較低的插入損耗,就要注意避免襯底電阻接近Rb(max)。然而,如果不對襯底電阻做特殊處理,這個值基本上屬于RF開關(guān)電路中晶體管的Rb值的典型范圍。對于標準CMOS工藝,取得較大的襯底電阻是不容易做到的,因此,降低襯底電阻是更好的方案。在版圖設(shè)計中,可通過增加襯底接觸來減小襯底電阻,從而達到進一步減小插入損耗的目的。

IL還可以用管子的柵寬(W)來表示,如(3)式。

一般來說,對于給定的工藝和版圖類型,Rbo、Cto和Rono可以被認為是固定的。所以柵寬的大小對插入損耗起著重要的影響:隨著柵寬的增大,導通電阻 Ron減小,從而使插入損耗減小;如果柵寬繼續(xù)增大,通過電容Ct耦合到襯底的信號也會增大,則插入損耗會隨著柵寬的增大而增大。所以,在仿真中需要確定最佳柵寬。

取并臂M3和M4的柵寬(WM3和WM4)接近WM1的一半。仿真結(jié)果表明,當WM1和WM2取200m且WM3和WM4取100m時,插入損耗最小。

另外,在MOS管的柵極增加電阻R的阻值也可降低插入損耗。仿真顯示,隨著柵極電阻的增大,插入損耗減小,但增加到10K以后,插入損耗減小的幅度就很小了,所以考慮到版圖面積,取柵極電阻的阻值為10K。

隔離度

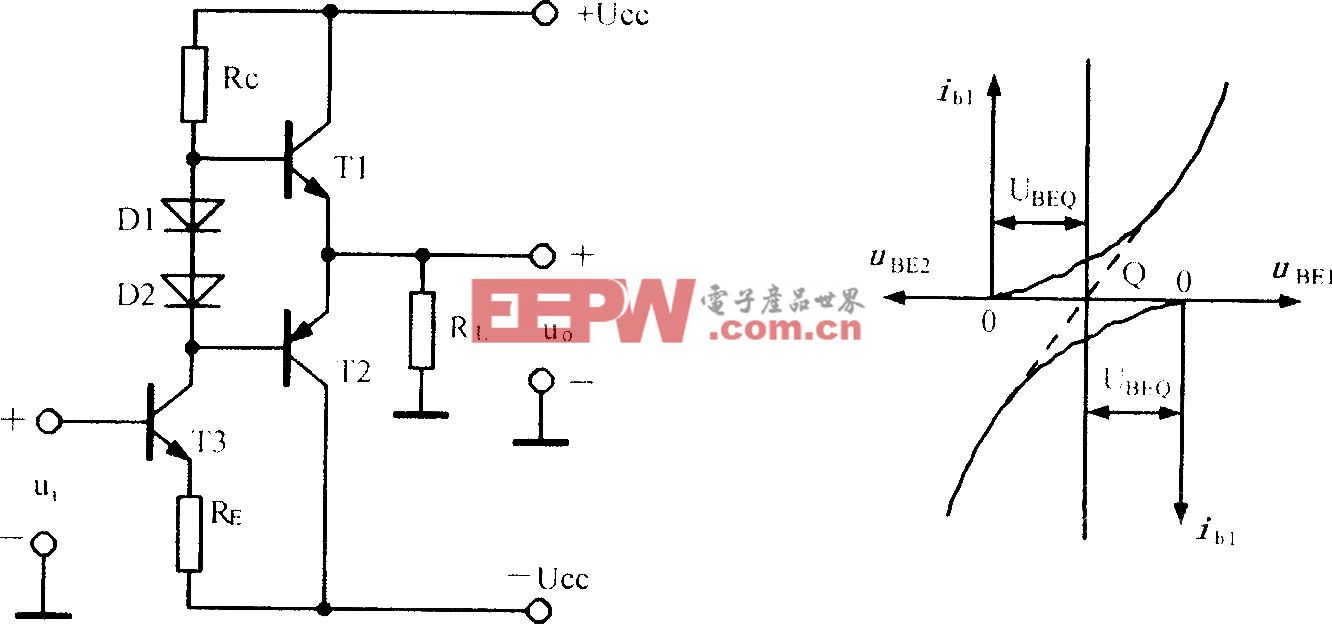

截止狀態(tài)下,開關(guān)的小信號等效電路如圖3所示。

圖3中,Ron表示并聯(lián)MOS管的導通電阻,Coff表示串聯(lián)MOS管在截止狀態(tài)下的漏/源極間電容。

依據(jù)S與Z參數(shù)之間的變換公式,可得到發(fā)射端(TX)和天線端(ANT)間的隔離度表達式:

(4) 式表明,通過使并聯(lián)的MOS管的導通電阻遠小于信號源的特征阻抗,使得從串聯(lián)的、處于截止狀態(tài)的MOS管泄漏出來的信號,可以通過并聯(lián)的MOS管導通到地,而不是泄漏到發(fā)送端,從而大大提高了隔離度。從仿真的結(jié)果看,加上并聯(lián)MOS管后,可以將隔離度提高10dB以上,而由此帶來的插入損耗的惡化卻可以忽略。此外,增加并聯(lián)MOS管的柵寬,也可以提高隔離度,但同時也會降低插入損耗和線性度,所以不宜取較大的柵寬。在本設(shè)計中,柵寬取為100m。

線性度

線性度,即功率處理能力,通常用P1dB來表示。CMOS開關(guān)的線性度通常受到以下兩種情況的制約:1.應截止的MOS管發(fā)生了導通,對于M3管,這種情況最嚴重;2. MOS管柵極電介質(zhì)性能不夠穩(wěn)定。

為了提高開關(guān)的線性度,本設(shè)計采用了兩種措施:1)在MOS管的漏、源極兩端都加上直流偏置電壓;2)給4個MOS管都加上柵極電阻R。

從仿真的結(jié)果看,增加柵極電阻可以使線性度改善5dB左右。

仿真結(jié)果

采用Cadence Spectre / Spectre RF仿真器進行仿真。在仿真過程中,分別對MOS管的柵寬和柵極電阻的阻值進行了優(yōu)化選取,并確定了偏置電壓和偏置電容。最終確定串聯(lián)MOS管M1和M2 的柵寬取200m,并聯(lián)MOS管M3和M4的柵寬取100m,柵極電阻R取10K,偏置電容C1和C2取5pF。仿真結(jié)果如圖4所示。

結(jié)語

本文分析了影響對稱式射頻收/發(fā)開關(guān)性能的因素,包括柵寬、導通電阻、襯底電阻、柵極電阻等。采用TSMC 0.35m CMOS工藝進行設(shè)計和實現(xiàn)。經(jīng)過優(yōu)化設(shè)計和仿真,獲得了插入損耗為1.0 dB、隔離度46.3 dB和1 dB壓縮點12.8 dBm的電路。該射頻收/發(fā)開關(guān)可以與應用于TD-SCDMA的全集成CMOS收發(fā)器集成在一起,構(gòu)成集成度更高、價格更低的收發(fā)器。

評論