基于SoC的抗窄帶干擾和自適應門限的基帶捕獲IP設計

3 IP的驗證和性能分析

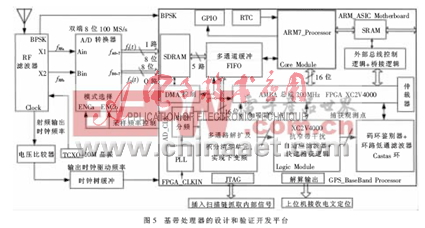

采用ARM公司的Integrator/AP ASIC Development Motherboard作為驗證平臺,濾波和捕獲跟蹤模塊是SoC中的一個IP,整個SoC以ARM7處理器為核心,通過AHB總線實現多個內部高速IP的互連,主要完成對接擴、下變頻、捕獲和濾波高速IP進行通信和解算;應用APB總線與外設進行交互,使用橋接器連接到AHB總線上,實現整個SoC的協同驗證。

GPS_BaseBand Processor的驗證平臺主要由三部分組成:Logic Module、 Core Module、ARM_ASIC Motherboard。其中Logic Module就是實現濾波和捕獲跟蹤的邏輯模塊,GPS基帶處理器的其他模塊可以通過加載多塊Logic Module來搭建整個設計。由于采用ARM公司的新型SoC設計開發平臺,可以將設計分割并行設計,并且通過AMBA總線將各個設計整合,因此提高了整個設計的效率。基帶處理器的設計和驗證開發平臺如圖5所示。

IP級驗證采用XILINX公司的XC2V4000高速芯片,經過synplify 8.5綜合后,設計使用了整個芯片資源的91%,103個乘法器和97個18kB的片上RAM,因此能夠滿足IP驗證需求。

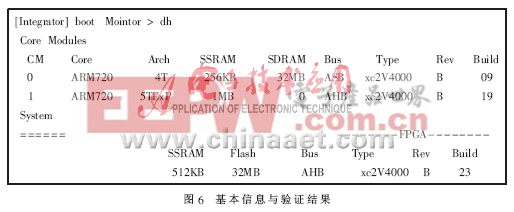

通過運行AP開發的軟硬件協同驗證環境,可以顯示當前AP系統驗證過程,核心板、邏輯板和基本外圍電路的狀態信息和驗證結果如圖6。

在加噪輸入點處,給輸入信號加入高斯白噪聲,在捕獲觀測點對信道的系統性能進行分析。假設每個碼片只采樣一個點,每個時刻都只有一個門限值,并且在N個碼片的累積過程中載波相位f保持不變的情況下,通過基帶處理器對6路下變頻信號接收和捕獲,在接收中心頻率為1 575.42MHz,接收電平為-137dBm的條件下,觀測到在對不同頻帶的窄帶干擾有效濾除同時,使信號在快衰減信號和信噪比突變的條件下捕獲的速度和精度能夠提高36%。

本文對于基帶處理器中捕獲跟蹤時信號的檢測概率的跳變和信號的粗同步時間優化的相關算法沒有更多考慮。下一步工作的重點是在此設計驗證環境下針對GPS 接收算法作進一步研究。

評論