基于串行RapidIo協議的無線通信基帶處理系統架構

1.2 RapidIO的關鍵技術

1.2.1 流量控制

RapidIO流量控制的首要目的是確保系統中數據流的平穩傳遞,以及避免事務因為被堵塞而無法完成。RapidIO在鏈路級定義了三種流量控制機制:重傳、減速和基于信用的流量控制。重傳機制是最簡單的機制,接收方在因為資源缺乏而來不及接收包時,會發出一個重傳控制符號作為響應,發送方接收到響應后將從該包處開始重傳直到其被接收方接收。減速機制是接收方通過發送減速控制符號,促使發送方在包間插入空閑控制符號,以增加發包間隔,從而達到降低發送流量的目的。基于信用的流量控制是接收方通過使用特定的控制符號向發送方指明每種事務流對應的緩沖空間信息,發送方根據該信息決定是否發包。

1.2.2 錯誤管理

RapidIO的工作頻率非常高,而在高頻率下工作很容易發生錯誤,因此需要強大的錯誤覆蓋機制,使其從硬件上確保RapidIO能夠準確地檢測到錯誤,并從中恢復。RapidIO發生的錯誤大體上可分為三類:第一類是接收方收到錯誤包;第二類是發生丟失事務錯誤;第三類是接口發生致命故障。 RapidIO結合重傳協議和循環冗余校驗碼提供了廣泛的錯誤檢測和恢復技術,同時還使用控制字符和響應定時器來減小系統中漏檢錯誤的可能性。

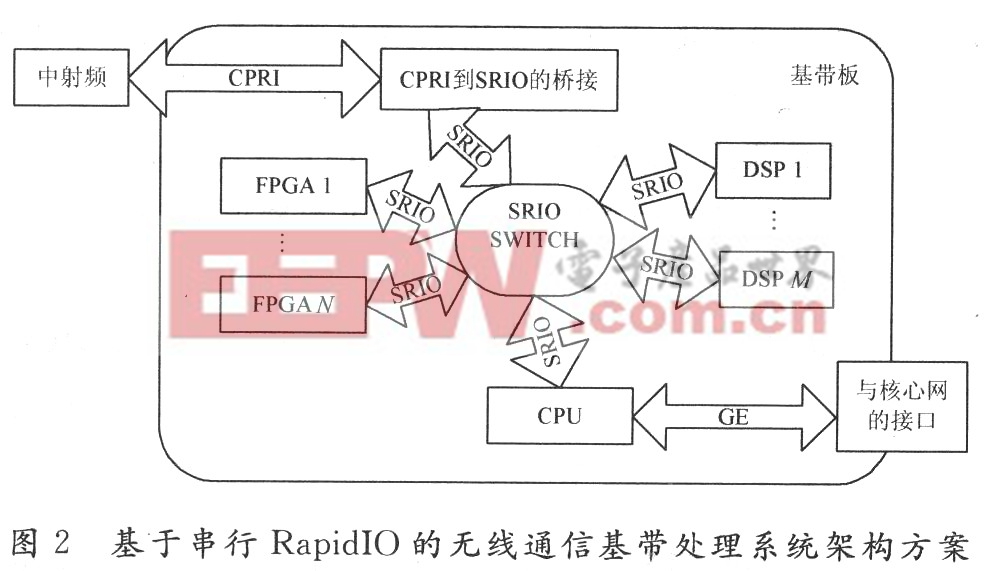

2 基于串行RapidIO的無線通信基帶處理系統架構方案

本文基于串行RapidIO所提出的無線通信基帶處理系統架構方案如圖2所示。在該方案中,CPU完成控制信息的生成以及MAC數據的調度,FPGA和DSP完成基帶數據的處理。各芯片均使用串行RapidIO與SRIO SWITCH芯片相連。

對于上行基帶處理而言,天線數據通過CPRI從射頻板傳輸到基帶板上,經過CPRI與SRIO(串行RapidIO)的橋接器后由SRlO SWITCH交換到FPGA或DSP開始處理。上行基帶處理通常需要在FPGA和DSP中進行FFT、信道估計、解調、解重復、解交織、解擾、譯碼以及數據校驗等處理。這些處理可以根據其在FPGA和DSP中實現的難易程度以及資源消耗率對實現器件進行選擇。經過校驗后,上行數據再通過 SRIOSWITCH被發往CPU進行MAC層的處理,處理完成的數據最后通過CPU的GE接口進入核心網。

對于下行處理而言,下行數據通過GE接口進入CPU,CPU再將數據發往相應的處理器件進行處理。當處理器件完成對下行數據的編碼、加擾、交織、IFFT等處理后,再通過CPRI與SRIO的橋接器發送到射頻板。

3 基于串行RapidIO的無線通信基帶處理系統架構方案的優點及測試驗證

基于串行RapidIO的基帶處理系統架構與傳統架構相比,具有諸多優點,本節將具體描述。同時,為了驗證所述優點以及系統架構的正確性,對系統進行了硬件實現,并在實現后的硬件上完成了相關的功能和流量測試。

3.1 優點分析

(1)系統具有很強的靈活性和可擴展性

靈活性和可擴展性是該系統架構最大的優點。不同的通信協議,其需要實現的功能以及數據的處理流程往往是不一樣的。即使是同一種協議,也會因為應用場景的不同而存在不同的需求。這些差異化的設計如果能在同一個硬件架構中實現,將會為設計者帶來巨大的便利。串行RapidIO是點對點的高速接口,圖2中各芯片可以通過SRIO SWITCH自由收發數據。同時,連接到SRIO SWITCH的處理器件個數可以在一定范圍內自由地增減,因此該架構可以實現不同的拓撲結構,以滿足不同的設計需要。

(2)任意兩個芯片間都可以進行數據的高速低延時傳輸

串行RapidIO協議1.3擁有兩種傳輸模式和三種傳輸速率。兩種傳輸模式分別為1x和4x,即發送和接收分別各有1對或4對差分線。差分線又有三種傳輸速率可供選擇,分別是:1.25Gb/s,2.5 Gb/s,3.125 Gb/s 。因此,芯片間的采用4x模式(1x模式)進行信號傳遞的最大流量可以達到12.5 Gb/s(3.125 Gb/s)。除去串行傳輸中的8 B/10 B編碼開銷、協議包開銷以及控制符號開銷后,有效載荷流量可以達到9 Gb/s(2.3 Gb/s)左右。9 Gb/s的流量可以輕松地滿足現代通信系統的需要。

(3)支持數據的分布式處理

隨著第三代無線標準的發展演進所帶來的更高的用戶數據率,基帶處理系統對數據處理性能的要求也在持續增加。為了解決芯片處理能力不能滿足系統發展需要的矛盾,在該架構中引入了分布式處理技術。由于RapidIO支持組播功能,數據可以通過圖2中的CPRI與SRIO的橋接器或某個FPGA以組播的方式同時向多個DSP傳送數據,每個DSP會根據自身的控制信息對數據進行不同的處理,完成處理后的各DSP會將數據發往同一個FPGA進行合并,從而完成對數據的分布式處理。

(4)上下行處理合并在同一個板上

將上下行處理合并在同一個板上是該架構的又一大特點。上下行的合并有利于對資源的充分利用,同時也可以根據場景的不同靈活地分配上下行資源,充分地體現了高性能、低消耗的特點,使其具有很強的現實意義。

(5)具有高穩定性和易于布局布線的特點

評論