一種基于FPGA和SC16C554實現多串口通信的方法

State 1:賦IsR寄存器地址給UART_A,置通道標志寄存器CS[2:O]=001(表示A通道);

State2:讀ISR,判斷中斷類型(04為接受數據準備好中斷),賦LSR寄存器地址給UART、A;

State3:讀LSR,判斷是否有數據(LSR[0]=1表示有數據在RHR內),賦RHR寄存器地址給UART A;

State4:讀RHR,讀取串口數據。

多通道工作時,可以通過增加狀態機狀態來實現。完成一個通道的讀數操作需要四個狀態,當四個通道同時工作時,狀態機的狀態需要增加到17個。其中Stare5~State8完成對通道B的操作;其中State9~State12完成對通道C的操作;其中State13~State16完成對通道D的操作。

3.3 讀時序設計

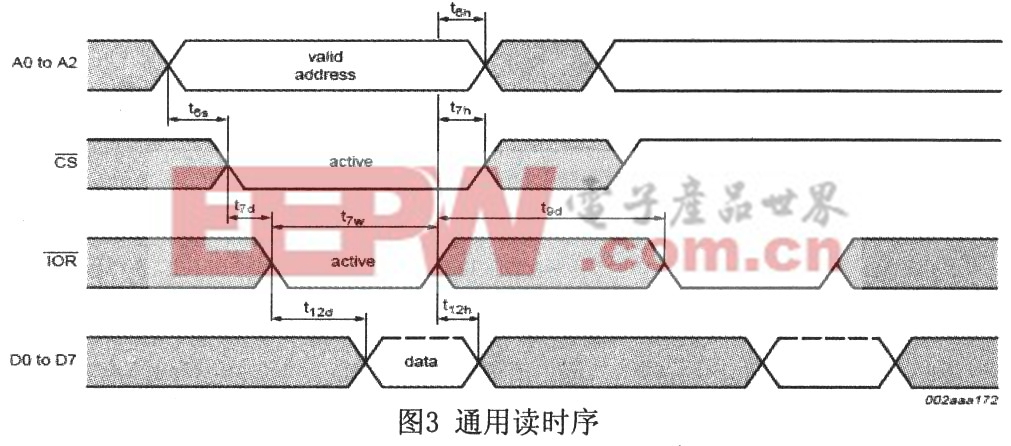

SC16C554的通用讀時序圖如下:本文引用地址:http://www.104case.com/article/157889.htm

其中t6s=0ns t6h=0ns t7h=0ns t7d=10ns t7w=26nst9d=20ns t12h=15ns都為最小值,t12d max=26ns由圖3可以看出:對串口進行一次讀操作所需的時間T=t6s+t7d+t7w+t9d所以T最小為56ns。本設計采用60MHz時鐘分頻出10MHz時鐘,在一個1OMHz時鐘周期(100ns)內完成一次讀操作。用6 0 MH z時鐘同步一個計數器cscount[2:0],在第一個6 0MH z時鐘的上升沿(cs_count=3’b000時)置CS為低,并賦對應的地址給UART A;在第二個60MHz時鐘的上升沿(cs_cout=3’b001時)置UART IOR為低;在第四個60MHz時鐘的上升沿(cs_count=3’b011時)置CS、UART IOR為高。這樣UART IOR有效時間為兩個時鐘周期(33ns),且比CS延時一個時鐘周期(17ns),完全滿足圖3讀時序的要求。

由圖2可知,由空閑狀態State0到完成一次串口數據的讀取,共需要500ns的時間。這樣多通道工作時連續完成四個通道的讀數操作共需2μs,遠小于單個通道連續兩個中斷產生的時間間隔65μs;這樣有效解決了多通道工作時,當讀取數據的過程中其它通道中斷丟失的問題。如:當讀通道A數據的過程中,通道B產生中斷請求;則狀態機完成通道A數據讀取返回到空閑狀態State0,檢測到INTB為高,狀態機進入下一個狀態(State5)進行通道B的數據接收。

4 測試結果及分析

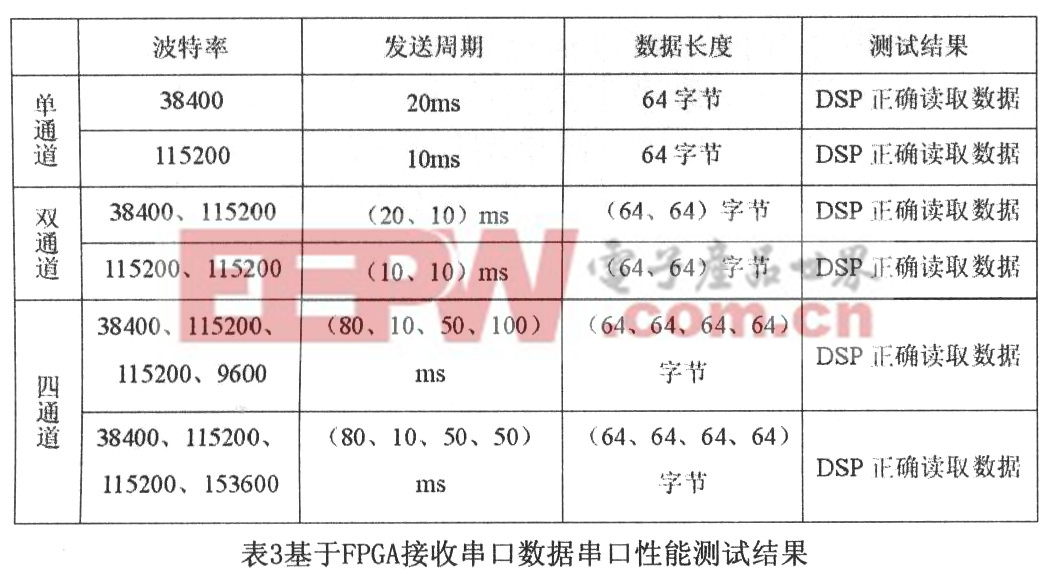

我們分別對兩種方案進行了測試,結果如下:表2為完全基于DSP接收和發送數據的通信性能測試;表3為基于FPGA接收串口數據的通信性能測試。

波特率發送周期數據長度測試結果

比較兩種方案的測試結果可以得出以下結論:

1單通道工作時:兩種方案的通信性能是一樣的。

2多通道同時工作時:由表2測試結果可以看出,每次發送的數據量過大、或發送周期較小時,由于DSP對串口芯片中斷請求的處理速度問題就會造成數據丟失。由表3測試結果可以看出,四通道工作時,發送數據長度為64字節,通道發送周期最小可達10ms;如果發送數據長度減小,通道發送周期還可以更小。該設計性能遠遠好于方案改進前完全基于DSP接收和發送數據的性能;能滿足系統實際工作的需要。

5 結束語

基于FPGA接收數據的設計有兩個突出的優點:1、極大提高了對串口中斷的響應速度,避免了多通道工作、完全基于DSP接收和發送數據時數據大量丟失的情況;2、完全可編程設置DSP中斷產生條件,解決了原來串口芯片只有1、4、8、14字節四個觸發深度的限制,可編程設置存儲空間范圍內的任意字節的觸發深度,大大減少了DSP的中斷數量,提高了DSP的工作效率。另外程序具有較強的可移植性,當設計需要修改時,只需修改少量代碼,有效降低了設計周期。

評論