軟件無線電技術與可重配置計算體系結構

1.技術趨勢

現代無線通信的主體是移動通信。參照ITU建議M1225,移動通信是在復雜多變的移動環境下工作的,因此必須考慮嚴重的時變和多徑傳播的影響。在現代無線通信系統中,特別是在碼分多址(CDMA)系統中,為了提高系統容量,提高系統靈敏度和在較低的發射功率下獲得較遠的通信距離,一般都希望使用智能天線與聯合檢測技術。

在許多公開發表的技術文獻中,都涉及到對智能天線的波束賦形算法的研究,其研究結論是功能越強則算法越復雜。然而在移動通信環境下,聯合檢測技術和波束賦形是必須實時完成的,且完成算法的時間只能以微秒計算。而受現代微電子技術水平的限制,在如此短的時間內,數字信號處理器(DSP)或專用芯片(ASIC)還不能實現過于復雜的實時處理。

另一方面,移動通信技術和標準還在不斷提出和更新,軟件無線電技術日益受到高度重視。美國FCC甚至發文要求各公司對此技術的應用提供方案。如何用DSP(數字信號處理器)或FPGA(現場可編程邏輯陣列)等其他可編程器件,在公共硬件平臺上解決各種不同制式的空間接口已成為很多世界各國通信公司研究的主要課題。

過去,無線通信系統的設計多采用靜態設計,只能在規定范圍內的特定頻段上使用專用調制器、編碼器和信道協議。即使是雙頻、三頻蜂窩電話也只在預先定義的兩個或三個標準之間切換。靜態設計通常是根據最壞情況的設計,在情況良好時就不能充分利用射頻頻譜。例如,若背景噪聲比最惡劣的情況小,就可能出現許多不必要的糾錯編碼,這樣就不能獲得最高的比特率。這種情況對無線應用系統的影響比有線應用系統更嚴重,因為無線傳輸更易于受噪聲、干擾和衰減的影響。理想的軟件無線電能動態適應傳輸系統的任一環節的變化,如調制、編碼、信道協議及帶寬,等等,并能夠適應實時性變化,最大程度地利用有效頻譜。已有專家預測,在未來幾年內,依靠傳統的專用芯片來制造移動通信無線設備的概念將受到重大沖擊。而且,軟件無線電不僅用于用戶終端,解決多模手持機的問題,它還將使用于無線基站。特別是在第三代移動通信技術和標準都還在不斷更新的最近幾年內,只有使用軟件無線電技術,才可能使產品跟上技術的發展,并適應不同的標準和環境、網絡通信負荷,以及用戶需求的變化。

在現階段軟件無線電結構體系的構建中,已有研究表明可編程邏輯器件具有較好的性能,尤其是針對高并行性運算比目前廣泛使用的DSP在性能上具有明顯的優勢,前者不但可以提高運算速度,更重要的是它可通過有效而靈活的設計方法提高系統硬件的整體工作效率,即盡可能使系統中所有邏輯資源處于有效工作狀態,降低系統功率。這是目前一些專用芯片以至DSP都無法比擬的。

2.軟件無線電技術的實現平臺

在軟件無線電技術的實現中,目前主流的硬件技術是通用信號處理器(以DSP為代表)和現場可編程邏輯陣列(以FPGA為代表)。雖然,現階段兩種技術作為軟件無線電實現平臺還都有各自的局限性,以下對比兩種技術在實現軟件無線電的一些特點:

由于軟件無線電技術基帶設計中大量使用乘加運算,DSP在完成這種乘加運算時, 一般需要進行以下操作:

1=>讀存儲器, 取操作數,取指令

2=>運算

3=>寫存儲器,存儲運算結果

為了提高運算速度,人們一般希望在一個指令周期中能夠多次進行存儲器讀寫操作,以盡量縮短非運算時間。

目前DSP廣泛采用了哈佛結構和改進的馮?諾伊曼結構,能夠支持在一個指令周期進行多次存取操作,這種體系結構適用于非關聯性順序算法的實現。當采用一個只能分時運行的數字信號處理器時,調度多個時間要求緊迫的任務需要非常復雜的編程。尤其是,當算法模塊關聯多個當前和過去及未來的狀態時,DSP的效率不高。這主要是由于DSP在處理一些并行和回饋數據流時,存在額外的等待時間。

隨著通信技術的發展,對系統性能的要求也在不斷增高,而設計高性能復雜DSP芯片的周期及半導體工藝的發展還沒有跟上需求的發展。于是,復雜通信系統往往使用多片DSP來提高系統性能。

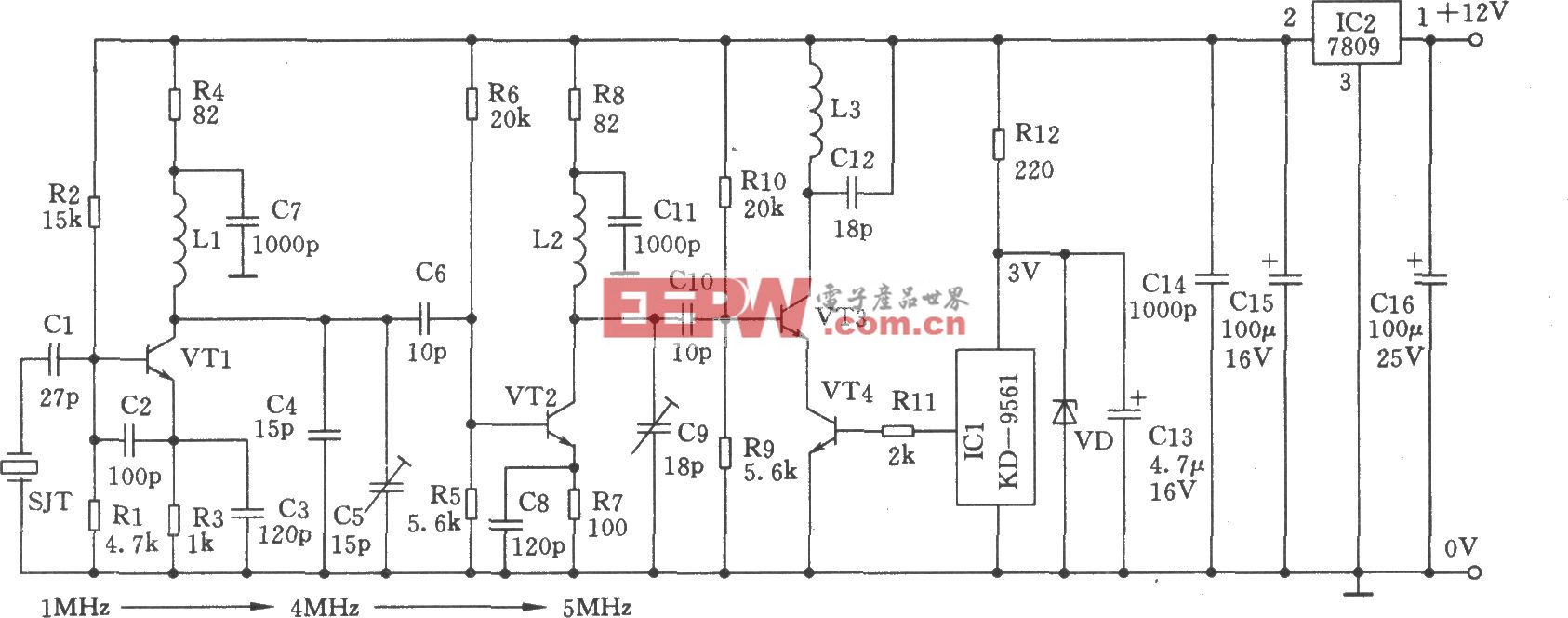

如圖2所示,典型的信號處理算法一般包括許多回饋環路和并行運算結構。通用DSP實現這類算法通常代碼效率并不高。

而用現場可編程門陣列(FPGA)實現上述算法,則可以克服上述設計的不足,這主要是由于FPGA提供了更大的設計靈活性。用FPGA設計軟件無線電時具有許多獨特的優勢,主要體現在:

2.1 設計靈活性與高性能

與DSP相比,FPGA有更大的靈活性,可根據算法特點自定制計算體系結構;利用并行性計算計算體系結構和合理的流水線設計可以實現高端DSP應用,且性能更高。使用FPGA構成多處理器計算體系結構,可將功能模塊很容易映射到獨立和并行的硬件節點上,實現任意多個并行數據處理路徑。避免了采用一個只能分時運行的數字信號處理器時,調度多個時間要求緊迫的任務所需的非常復雜的編程。

評論