RMII模式以太網PHY芯片DP83848C的應用

摘要:介紹了美國國家半導體公司的PHY芯片DP83848C的功能特性;給出了在RMII(Reduced Medium Independent Interface,精簡的介質無關接口)模式下的硬件電路及軟件設計,以及在PCB布局布線過程中的注意事項。該設計為嵌入式系統中以太網底層的軟硬件設計提供了參考,也為TCP/IP協議在嵌入式系統上的實現提供了硬件平臺。

關鍵詞:RMII;DP83848C;以太網;物理層;介質訪問控制

引言

DP83848C是美國國家半導體公司生產的一款魯棒性好、功能全、功耗低的10/100 Mbps單路物理層(PHY)器件。它支持MII(介質無關接口)和RMII(精簡的介質無關接口),使設計更簡單靈活;同時,支持10BASE~T和100BASE-TX以太網外設,對其他標準以太網解決方案有良好的兼容性和通用性。

MII(Medium Independent Interface)是IEEE802.3u規定的一種介質無關接口,主要作用是連接介質訪問控制層(MAC)子層與物理層(PH-Y)之間的標準以太網接口,負責MAC和PHY之間的通信。由于MII需要多達16根信號線,由此產生的I/O口需求及功耗較大,有必要對MII引腳數進行簡化,因此提出了RMII(Reduced Medium Independent Interface,精簡的介質無關接口),即簡化了的MII。

1 硬件設計

1.1 電路設計

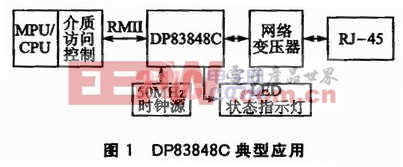

DP83848C的收發線路各是一對差分線,經過變比為1:1的以太網變壓器后與網線相連。以太網變壓器的主要作用是阻抗匹配、信號整形、網絡隔離,以及濾除網絡和設備雙方面的噪音。典型應用如圖1所示。

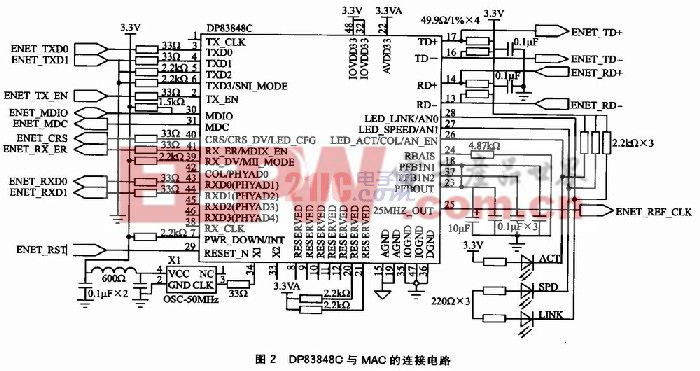

圖2是DP83848C與MAC的連接電路。其中,Xl為50 MHz的有源振蕩器。

1.2 PCB布局布線

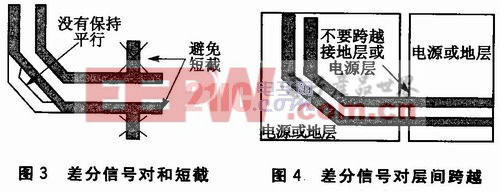

布局方面,精度為1%的49.9 Ω電阻和100 nF的去耦電容應靠近PHY器件放置,并通過最短的路徑到電源。如圖3所示,兩對差分信號(TD和RD)應平行走線,避免短截,且盡量保證長度匹配,這樣可以避免共模噪聲和EMI輻射。理想情況下,信號線上不應有交叉或者通孔,通孔會造成阻抗的非連續性,所以應將其數目降到最低;同時,差分線應盡可能走在一面,且不應將信號線跨越分割的平面,如圖4所示。信號跨越一個分割的平面會造成無法預測的回路電流,極可能導致信號質量惡化并產生EMI問題。注意,圖3和圖4中,陰影部分為錯誤方法。

評論