超高速雷達(dá)數(shù)字信號(hào)處理技術(shù)

3.一種高速實(shí)時(shí)多功能數(shù)字脈沖壓縮系統(tǒng)的實(shí)現(xiàn)

采用頻域法實(shí)現(xiàn)了一個(gè)高速實(shí)時(shí)多功能數(shù)字脈沖壓縮系統(tǒng);系統(tǒng)的體系結(jié)構(gòu)就采用圖3的方式.這里,系統(tǒng)實(shí)時(shí)性的關(guān)鍵問(wèn)題是FFT芯片的速度;我們選擇了可在98us時(shí)間內(nèi)完成1024點(diǎn)FFT的高速專用FFT芯片.系統(tǒng)中存儲(chǔ)參考碼的EPROM可以存放不同的匹配濾波器參數(shù),只要變換EPROM的地址,就可以實(shí)現(xiàn)對(duì)不同信號(hào)形式的脈沖壓縮.因此,這是一種高速、實(shí)時(shí)、多功能的數(shù)字脈沖壓縮系統(tǒng).

七、超高速雷達(dá)信號(hào)發(fā)生器/回波模擬器的實(shí)現(xiàn)

1.直接數(shù)字合成法實(shí)現(xiàn)超高速信號(hào)發(fā)生器

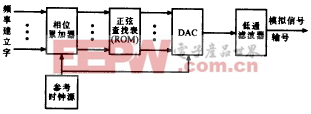

DDS的基本原理如圖4所示[20],其核心內(nèi)容是超高速D/A變換器和一個(gè)正弦查找表.這里,正弦查找表存儲(chǔ)了一個(gè)完整的正弦波在不同相位上的幅度值;因此,只要改變正弦查找表的尋址方式,就可以獲得不同類型的數(shù)字信號(hào);再經(jīng)過(guò)DA變換器和低通濾波器,就是所需要的模擬信號(hào).

圖4 DDS技術(shù)的原理框圖 2.超高速雷達(dá)回波模擬器的實(shí)現(xiàn) |

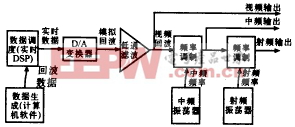

圖5 雷達(dá)回波模擬器的原理框圖 (3)超高速雷達(dá)回波模擬器的實(shí)現(xiàn) 采用圖6介紹的方法實(shí)現(xiàn)了一個(gè)超高速雷達(dá)回波模擬器.模擬器的時(shí)鐘頻率為250MHz,因此模擬器的輸出頻率最高可達(dá)125MHz(圖6). |

圖6 超高速雷達(dá)回波模擬器的實(shí)現(xiàn)框圖 3.采用超高速雷達(dá)回波模擬器產(chǎn)生多種雷達(dá)發(fā)射信號(hào) |

評(píng)論