高速DAC簡化無線設計

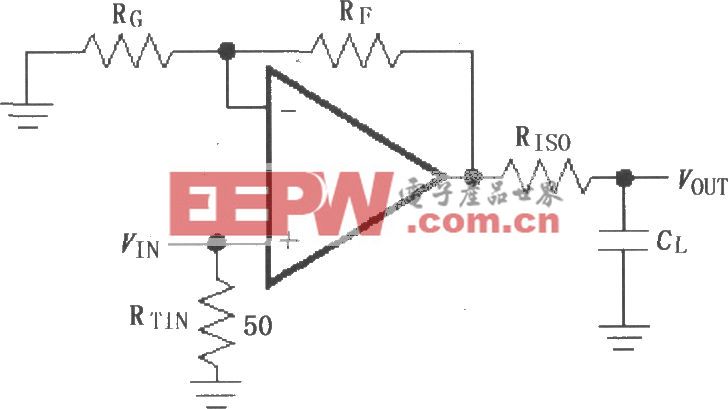

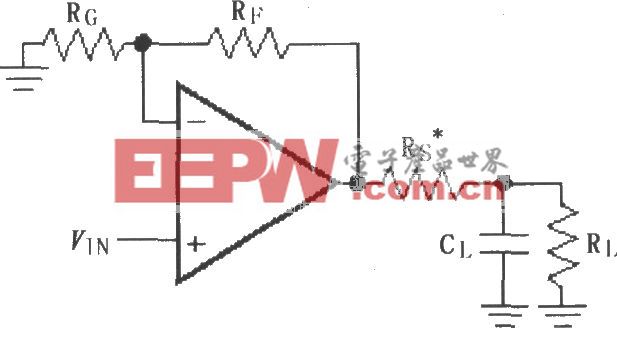

在發射機設計中,插值濾波器可通過將DAC鏡像移出帶外,來降低數模轉換器(DAC)與上變頻級之間的模擬濾波要求。

本文引用地址:http://www.104case.com/article/156741.htm同時,在高速DAC中集成使用數控振蕩器(NCO)的精密復雜調制功能,可進行更高中頻(IF)信號合成,這樣就無需在RF鏈中配置鏡像抑制濾波器,或者可降低對該濾波器的要求。

IF頻率進行微調同樣可降低生成發射本振(LO)的要求。 利用NCO可滿足通信系統對于信道柵或頻率步進大小的要求,不必通過發射(TX)本振鎖相環(PLL)的分頻比吸收該步進大小,否則會導致更多的小數雜散。

線性度和效率

為了幫助實現發射機效率,可利用數字基帶處理糾正通信系統中RF/微波放大器、電纜和其他器件的線性缺陷。

數字預失真(DPD)和波峰因素降低(CFR)等先進數字算法,也將成為最受歡迎的功率放大器(PA)線性化技術,并將發射機效率從低于10%提高到超過40%。

數字預失真算法需要一個觀測接收機,通過其中的高帶寬ADC對PA輸出的耦合版本進行下變頻處理。

發射波形的數字版本與接收波形相比較,由自適應算法計算或更新一系列參數,以便預加載下一個發射波形。

由于融合了自適應算法,PA得到線性化處理,從而使輸出失真顯著降低。與其他模擬線性化方法(例如前饋線性化)相比,速度提高以及向精細線工藝過渡,都會使多天線發射系統的數字預失真更具可伸縮性。

用于產生信號的DAC

超高速DAC已經成為現代基站和各類無線基礎設施(WIFR)系統設計中的主要信號發生器。現在,這些DAC也能實現以前由各種附加電路元件(包括基帶處理器)完成的很多功能。

這賦予設計師更大的靈活性,使設計更簡單、成本和功耗更低,而且還提高了信號質量。 隨著數字接口更多地采用低電壓差分信號(LVDS),數據速率可達到1200兆采樣/秒甚至更高,同時功耗和電源電壓保持較低水平。DAC采用高輸入數據速率有助于增加發射路徑輸入帶寬,從而支持更高階數字預失真(DPD)算法或更寬的校正帶寬。

LVDS輻射更小,能提供更好的抗擾度和時序。

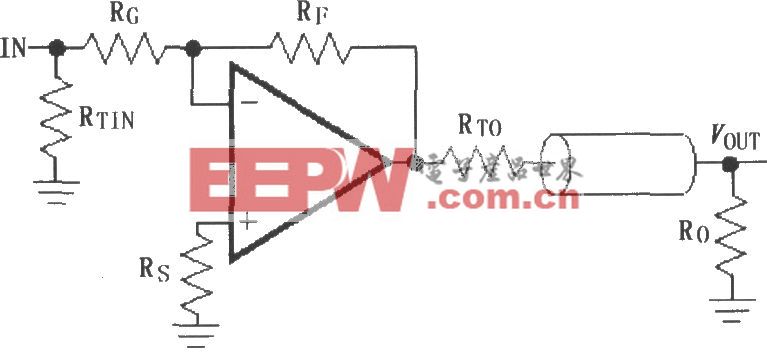

現在,信號處理DAC可以在復雜的中頻(IF)直接變頻架構中工作, 并提供經過完全調制的IF I和Q信號,可直接通過模擬正交調制器和功率放大器(PA)送入天線,無需進行額外的信號調制。 DAC內置LVDS接口能提供更大的靈活性,支持標準32位總線的二分之一或四分之一寬度配置,從而盡量減少小系統中的互連。

全球的先進多載波無線和寬帶通信設備都需要較高的數據速率和復雜的調制方案。

對于耗費數百億英鎊的無線基礎設施,信號鏈中的每一個器件都需要盡可能地優化,以提高性能、降低成本并減小功耗。

在發射機設計中,插值濾波器可通過將DAC鏡像移出帶外,來降低數模轉換器(DAC)與上變頻級之間的模擬濾波要求。

同時,在高速DAC中集成使用數控振蕩器(NCO)的精密復雜調制功能,可進行更高中頻(IF)信號合成,這樣就無需在RF鏈中配置鏡像抑制濾波器,或者可降低對該濾波器的要求。

IF頻率進行微調同樣可降低生成發射本振(LO)的要求。 利用NCO可滿足通信系統對于信道柵或頻率步進大小的要求,不必通過發射(TX)本振鎖相環(PLL)的分頻比吸收該步進大小,否則會導致更多的小數雜散。

線性度和效率

為了幫助實現發射機效率,可利用數字基帶處理糾正通信系統中RF/微波放大器、電纜和其它器件的線性缺陷。

數字預失真(DPD)和波峰因素降低(CFR)等先進數字算法,也將成為最受歡迎的功率放大器(PA)線性化技術,并將發射機效率從低于10%提高到超過40%。

數字預失真算法需要一個觀測接收機,通過其中的高帶寬ADC對PA輸出的耦合版本進行下變頻處理。 發射波形的數字版本與接收波形相比較,由自適應算法計算或更新一系列參數,以便預加載下一個發射波形。

由于融合了自適應算法,PA得到線性化處理,從而使輸出失真顯著降低。與其它模擬線性化方法(例如前饋線性化)相比,速度提高以及向精細線工藝過渡,都會使多天線發射系統的數字預失真更具可伸縮性。

用于產生信號的DAC

超高速DAC已經成為現代基站和各類無線基礎設施(WIFR)系統設計中的主要信號發生器。現在,這些DAC也能實現以前由各種附加電路元件(包括基帶處理器)完成的很多功能。

這賦予設計師更大的靈活性,使設計更簡單、成本和功耗更低,而且還提高了信號質量。

隨著數字接口更多地采用低電壓差分信號(LVDS),數據速率可達到1200兆采樣/秒甚至更高,同時功耗和電源電壓保持較低水平。DAC采用高輸入數據速率有助于增加發射路徑輸入帶寬,從而支持更高階數字預失真(DPD)算法或更寬的校正帶寬。

LVDS輻射更小,能提供更好的抗擾度和時序。

現在,信號處理DAC可以在復雜的中頻(IF)直接變頻架構中工作, 并提供經過完全調制的IF I和Q信號,可直接通過模擬正交調制器和功率放大器(PA)送入天線,無需進行額外的信號調制。 DAC內置LVDS接口能提供更大的靈活性,支持標準32位總線的二分之一或四分之一寬度配置,從而盡量減少小系統中的互連。

評論