基于AD9954的多模式調制器的設計

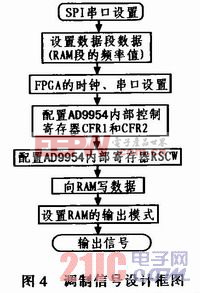

5.2 FPGA的編程設計

首先利用FPGA制作1個ROM表,該表中存入的是一組相位信息或者頻率信息,然后通過時鐘的分頻及譯碼電路獲得信息表的地址,將對應地址的內容作為輸出,最后通過1個判決電路(二選一電路)來控制輸出模式。ROM表中的地址內容可以控制AD9954對實際相位值或實際頻率值的選擇。

由于FPGA的內部時鐘存在一定的不穩定性,因此在這里選用外部穩定的晶振作為輸入,一方面提供了穩定的時鐘輸入,另一方面又可以減小FPGA內部寶貴資源的使用。

6 實驗輸出波形的時域和頻域分析圖

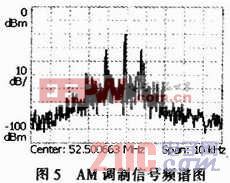

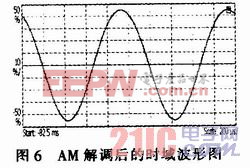

6.1 AM信號測試分析

AM系統頻域頻譜結構和時域解調波形測試結果分別如圖5、圖6所示。

AM載波頻率設置為52.5 MHz,實際測得的中心頻率為52.500 663 MHz,頻率誤差為0.000 663/52.5=1.263x10-5,誤差在系統規定的范圍內。

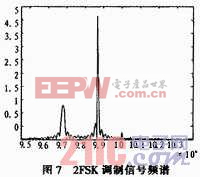

6.2 2FSK和4PSK信號測試分析

在該平臺下生成的FSK和QPSK頻譜如圖7、圖8所示。

2FSK信號是設置AD9954在Direct Switch模式下進行測試的,AD9954的系統時鐘為200 MHz,RAM0和RAM1設置的頻率值分別為9.7 MHz和9.9 MHz。設PS0=0,根據基帶信號0或1改變PS1的值為0或1即可產生2FSK信號。將2FSK信號波形數據采集并存儲后對其做FFT變換,畫出其頻譜圖如圖6所示,可見在9.69 MHz和9.88MHz有兩根譜線,證明采集到的為2FSK信號。

4PSK信號是設置AD9954在Direct Switch模式下進行測試的,AD9954的系統時鐘為200 MHz,RAM0、RAM1、RAM2和RAM3設置的頻率值分別為9.7 MHz、10.3 MHz、10MHz和10.9 MHz。根據基帶信號的0或1或2或3改變PS1和PS0的值即可產生4FSK信號。

7 結束語

本文介紹了采用先進DDS技術的AD9954性能特點和工作原理及過程,利用其可編程幅度、頻率、相位給出了AD9954在高速調制信號系統中的應用方案,從而較方便地實現基于軟件無線電技術的各種調制信號。采用超高速、先進DDS技術的數字中頻處理技術的方法,構建AD9954硬件實現平臺,結合相應的數字處理軟件和控制軟件,可獲得調幅、噪聲調頻、FSK、PSK等多種調制信號。本文提出的硬件實現方案,為產生多模式信號提供了硬件平臺,具有較好的應用價值。

評論