一種改進型的時分多址的實現方法

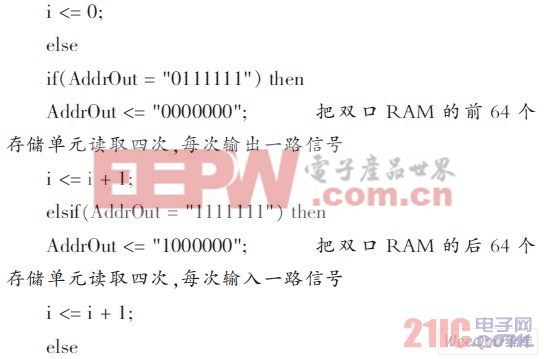

在端口B輸入時鐘elk12288的每個下降沿,端口B輸入地址AddrOut都遞增1,則在elk12288的上升沿,根據例化的雙口RAM的IP核,相應的地址空間中的數據將通過Dout被讀出來。本文引用地址:http://www.104case.com/article/156579.htm

依次將輸出數據以時分多址的幀格式傳輸出去。

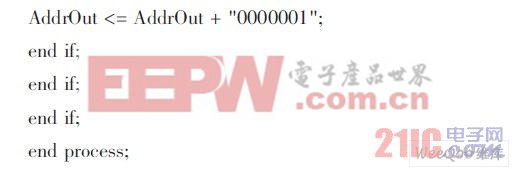

3 仿真結果

用ModelSim se 6.2b對程序進行仿真,在48 kHz的時鐘周期內,給第1路輸入源的64位輸入信號為0x1111111111111111,第2路輸入源的64位輸入信號為0x2222222222222222,第3路輸入源的64位輸入信號為0x3333333333333333,第4路輸入源的64位輸入信號為0x4444444444 444444。仿真結果如圖2所示。

圖2 仿真結果

由仿真圖可以看出,在一個48 kHz的時鐘周期內,TDMA_OUT,即時分多址幀格式的輸出為0x11111111111111112222222222222222333333 33333333334444444444444444,即每一幀被分成了4個時隙,4路輸入信號在每一幀中占用各自的時隙進行傳輸,通過該仿真結果,可以驗證該方法的可用性。

將VHDL語言程序通過ISE10.1綜合,布局布線后,通過JTAG線纜下載到XC3S500E中進行電路板上的測試,再次驗證了該方法的正確。

通過ISE綜合后,可以看到程序所占用的芯片資源如下表所示。

表1 芯片資源情況

從表中的數據可以看出,通過使用一個BRAM從而節約了大量的資源,FPGA芯片資源的重要指標Slices僅僅占用了15個,LUTs僅僅用了29個,可見,該方法所占用的FPGA資源極少,達到了設計目標。

4 結論

本文研究了FPGA實現時分多址的一種改進型的方法,通過使用FPGA芯片內部的雙口RAM,利用IP核,實現了多路信號轉換成時分多址幀格式信號進行傳輸,根據所占資源的統計數據,可以看到在完成相同功能的前提下,該方法相比于已有的方法,確實能大量節省FPGA芯片的邏輯資源,從而使單片FPGA能完成更多的邏輯功能。但是,此方法會占用一部分雙口RAM,在雙口RAM資源緊張的時候不是太適用。

用ModelSim SE 6.2b對FPGA程序進行了仿真,并且將程序下載到電路板上進行了驗證,證實了該方法的可用性。

評論