基于ADF4360-2的1 GHz頻率合成器設計

2 頻率合成系統電路設計

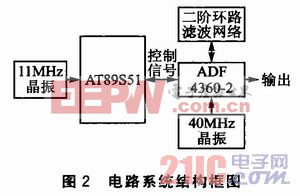

通過外部頻率源信號和單片機控制信號,14位可編程參考R分頻器對外部頻率源信號分頻后,得到參考頻率送至鑒相器。控制信號由時鐘信號CLK、數據信號DATA和使能信號LE組成。在CLK的控制下,串行輸入24位數據信號,暫時存放在24位數據寄存器中。在接收到使能信號LE后,先前輸入的24位數據根據地址位到達對應的鎖存器。ADF4360-2的主分頻比N由雙模預分頻器(P/P+1)、可編程5位A計數器及13位B分頻器實現,算法為N=B×P+A,輸出頻率為fVCO=(B×P+A)×fREFIN/R,通過設置A、B、R三個控制字寄存器的控制字來實現對鎖相環的控制。該芯片外圍只需添加環路濾波器,根據輸出頻率大小選擇合適的參數,即可輸出較穩定的頻率。電路系統結構框圖如圖2所示。本文引用地址:http://www.104case.com/article/156398.htm

環路濾波網絡具有低通特性,它主要是抑制鑒相器輸出電壓中的載頻分量和高頻噪聲,降低由VCO控制電壓不純而引起的寄生輸出。圖2中所示的環路濾波網絡可利用ADI公司提供的專用設計與仿真工具軟件ADI simPLL進行仿真、設計。

3 芯片配置程序設計

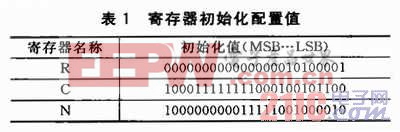

本電路設計中,ADF4360-2的PFD輸入頻率為1 MHz,因此參考時鐘分頻R=40。由公式fVCO=(B×P+A)×fREFIN/R,可計算出N為11 250,雙模預頻器設置為P/(P+1)=32/33,計數器A設置為8,計數器B設置為32。根據ADF4360-2芯片資料,3個控制寄存器初始化設置為R寄存器00000A1H,C寄存器8FF12CH,N寄存器803E42H,配置值如表1所列。

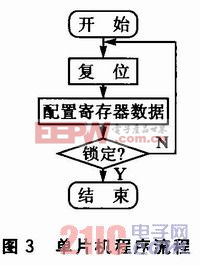

單片機通過提供時鐘信號CLK、數據信號DATA和使能信號LE,對ADF4360-2內部寄存器進行配置,使得VCO輸出所需頻率的信號,同時負責對ADF4360-2的鎖定標志進行檢測,如果檢測已經鎖定,則配置數據工作完成。單片機程序流程如圖3所示。

結語

本文介紹了利用鎖相頻率合成芯片ADF4360-2設計1 GHz信號的輸出方法,給出了電路系統結構框圖以及單片機程序流程。由于ADF4360-2內部集成VCO,外部通過單片機I/O口寫入控制字,因此該系統具有外圍電路簡單、調試方便、功耗和成本低等特點,可廣泛應用于各種電路系統中。

評論