基于DSP平臺的多音平行體制調制端的實現

摘要 以32音并行體制為例,利用DSP平臺實現了多音并行體制的調制端,給出了其主要模塊的具體實現方法。由于并行體制技術成熟、成本低、高性價比對提高數據傳輸速率、消除多徑衰落有益。

關鍵詞 多音并行體制;調制;傅里葉變換;DSP

短波通信中常采用多音并行和單音串行兩種體制來進行高速數據的傳輸。單音串行體制僅采用一個載波,串行發送數據信號。由于每個碼元占據了整個頻譜,碼元寬度窄,當傳輸高速數據時,實現復雜,且碼間串擾嚴重。而多音并行體制的主要思想就是把高速串行信道分裂成許多低速的并行信道,以適應短波信道低速傳輸的特性,在每個子信道上傳送一個副載波,采用頻分正交調制,用多個副載波并行傳輸的方法提高速率。并行體制的傳輸,是采用加寬碼元寬度,使其遠大于多徑時延,消除多徑衰落的影響。并行體制技術成熟、成本低,具有較高的性價比。本文以32音體制為例說明短波并行體制調制端的DSP具體實現方法。

1 32音并行體制調制端的設計

本并行體制在音頻頻帶內采用32個正交副載波音,對比特同步數據傳送采用正交差分相移鍵控(QDPSK)調制。

具體設計要求:

(1)在數據輸入端口接收不同速率的串行二進制數據:300 b·s-1,600 b·s-1,1 200 b·s-1;

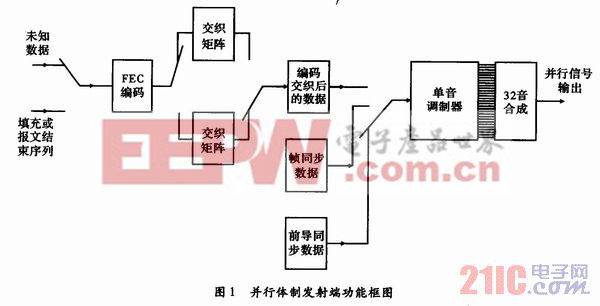

(2)對接收到的二進制數據完成前向糾錯(FEC)編碼和交織;

(3)每個單音上采用QDPSK調制;

(4)采用32個正交載波音,每個音相隔56.25 Hz;

(5)采用某種分集方式。

圖1為多音并行體制下發射端功能框圖。

2 軟硬件平臺介紹

本文實現多音并行調制端的硬件平臺如圖2所示,主要由計算機PC、DSP-TMS320C6416、A/D芯片TLV320AIC20組成。DSP通過多通道緩沖串口1(McBSP1)與計算機相互通信,同時通過多通道緩沖串口0(McBSPO)與TLV320AIC20相互通信。

本平臺采用的TMS320C64xx系列是2000年3月TI正式發布的定點系列,主頻1.1 GHz,處理速度接近9 000 MI·s-1總體性能比C62xx提高了10~15倍。

TLV320AIC20是TI公司生產的一款低功耗高性能的雙通道A/D芯片,可含有兩個16位A/D通道和兩個16位D/A通道,完成模擬與數字話音的轉換工作,軟件可編程寄存器內含有6種可編程的控制寄存器,配置方便。

軟件平臺采用CCS(Code Composer Studio)系統,其包含一整套用于開發和調試嵌入式應用的工具。它包含適用于每個TI器件系列的編譯器、源碼編輯器、項目構建環境、調試器、描述器、仿真器以及多種其它功能。

3 并行體制關鍵模塊的具體實現

3.1 核心模塊-FFT

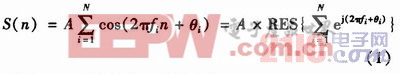

由于發送信號是一組余弦函數的疊加。假設信號是由一組N個頻率為f1,f2,f3,…,fN,初始相位為θ1,θ2,θ3,…,θN,幅度為A的余弦信號,故其疊加后的信號為

其中,RES[]是取函數的實部。

從式(1)中可以看出,利用反傅里葉變換(IFFFT)可以方便地產生前導序列和生成調制信號方便。同時反傅里葉變換在DSP中運算量不大,并可以直接調用傅里葉變換,將輸入信號的格式稍加處理即可得到反傅里葉變換的結果。

評論