基于USB通信的FPGA高速數據采集系統

1.3 USB器件

USB接口使用方便,連接簡單,但是通信協議很復雜。因此,USB外設必須使用控制器芯片,管理數據通信USB控制器采用集成了8051單片機的CY7C68013A控制器芯片,該芯片遵從USB 2.0規范,有較快的傳輸速度,是目前比較通用的一種USB控制芯片。

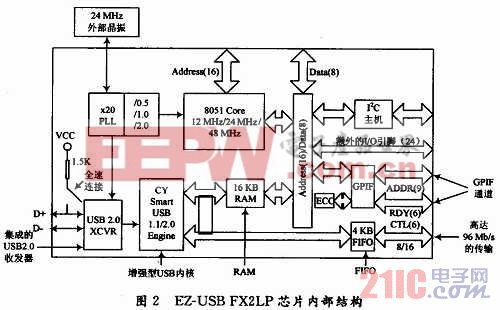

CY7C68013A是Cypress公司EZ-USB FX2LP系列芯片中比較經典的一款USB控制器,其內部結構如圖2所示。其中,主要包括USB 2.0收發器、串行引擎(SIE)、增強型8051內核、16 KB的RAM、4 KB的FIFO存儲器、I/O接口、數據總線、地址總線和通用可編程接口(GPIF)。本文引用地址:http://www.104case.com/article/156123.htm

EZ-USB FX2LP擁有非常獨特的結構,其串行接口引擎(SIE)負責完成串行數據的解碼、差錯控制、位填充等與USB有關的功能。串行接口引擎(SIE)能夠實現大部分的功能,從而減輕了嵌入式增強型8051的負擔,簡化了USB固件程序的開發。

2 系統軟硬件實現

2.1 A/D轉換

系統通過PINFET光電轉換為單端模擬信號,而A/D轉換器AD7356是差分輸入方式,所以需要對輸入方式進行轉換。AD7356說明書中給出了詳細的轉換電路,按說明連接即可。由于AD7356供電電源為2.5 V,所以和FPGA之間的連接需要調整AD7356的信號電平,使得輸出電平與FPGA的3.3 V電平兼容。在電路設計時,可以通過將AD7356的Vdriver引腳連接到3.3 V,這樣使得輸出信號電平為3.3 V。

系統采用的AD7356采樣頻率由輸入時鐘信號決定,而采樣通過使能引腳CS控制。在設定好采樣頻率后,A/D轉換程序主要依靠對CS信號控制,并對輸入得兩路信號串并轉換即可。

2.2 數據緩存

數據緩存主要是利用FPGA內自帶的塊RAM對多路信號進行排序、存儲,然后按USB數據包大小打包傳輸,因此對于硬件(FPGA)不再多做介紹。

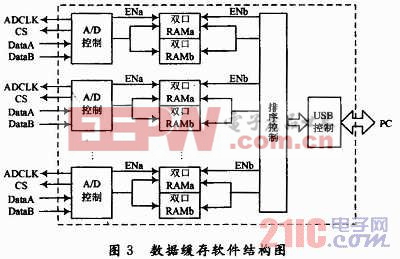

數據緩存的軟件實現主要依靠FPGA內的雙口RAM IP核。雙口RAM由于有2個單獨的數據輸入和輸出口,所以可以調節輸入輸出端口的速度,使得數據讀取與輸入速度可以方便的控制。另外,由于本系統有多路光信號,所以FPGA內還需要對各個雙口RAM的讀取進行控制,對各路信號讀取順序進行,其軟件結構圖如圖3所示。每路A/D都有兩個RAM輪流存儲采集數據,一方面避免RAM出現數據溢出,保證數據不丟失;另一方面可以通過將RAM大小設定與USB數據包大小一致,使USB傳輸的控制簡單。

評論