基于無線通信技術的數據記錄系統

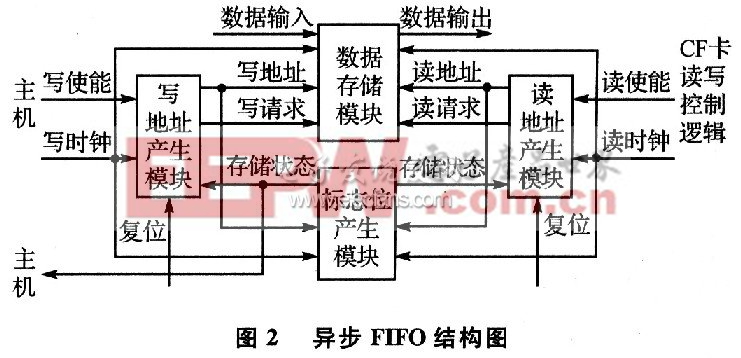

數據記錄設備的實時性強、數據量大。為了提高數據傳輸速度、避免數據堵塞,利用FPGA硬件設計上的靈活性,在其內部構建了一個寬度為16位、深度為512的異步FIFO模塊,作為DSP與CF卡之間數據傳輸的中繼站。

異步FIFO的結構圖如圖2所示。它包括4個模塊:數據存儲模塊、寫地址產生模塊、讀地址產生模塊和標志位產生模塊。FIFO的讀寫采用讀時鐘和寫時鐘兩個時鐘。寫時鐘同步的信號有寫地址產生模塊生成的寫請求和寫地址;讀時鐘同步的信號有讀地址產生模塊生成的讀請求和讀地址。寫使能和讀使能分別由DSP與FPGA數據傳輸控制邏輯和CF卡讀寫控制邏輯生成。標志位產生模塊由讀寫地址關系生成FIFO存儲狀態標志,并反饋給主機DSP。DSP通過查詢該標志來控制與FPGA的數據傳輸。

3.1.2 CF卡讀寫模塊

CF卡讀寫模塊分為CF卡讀控制模塊和CF卡寫控制模塊。CF卡讀或寫模塊的設計具有相似性。這里僅介紹寫CF卡的工作過程。

首先,設置CF卡的屬性寄存器。CF卡有4個屬性寄存器,通常只需設置“配置選擇寄存器”以選擇CF卡的讀寫模式。CF卡的讀寫模式有3種:I/O模式、Memory模式和True IDE模式。本設計使用16位的Memory模式讀寫CF卡。Memory模式是CF卡默認的讀寫模式,所以在CF卡初始化過程中不需要設置“配置屬性寄存器”。

其次,設置CF卡的任務文件寄存器。本設計中使用的任務文件寄存器有:數據寄存器、扇區數寄存器、扇區號寄存器、低柱面號寄存器、高柱面號寄存器、驅動器選擇/磁頭寄存器和狀態/命令寄存器。對它們進行沒置,可選擇扇區尋址方式,設定每次讀寫的扇區數和邏輯尋址地址,并獲取CF卡狀態以及輸入讀寫命令。

CF卡的尋址方式與計算機的硬盤操作方式類似。扇區的尋址方式有兩種:物理尋址方式(CHS)和邏輯尋址方式(LBA)。本設計使用LBA尋址,對應28位LBA地址。

磁頭寄存器存放LBA地址的27~24位;柱面號寄存器存放LBA地址的23~8位;扇區號寄存器存放LBA地址的7~0位。

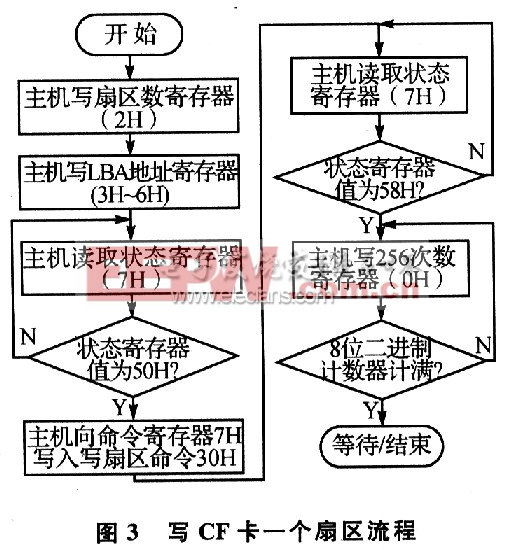

寫CF卡一個扇區的流程如圖3所示。每次向CF卡存儲數據時,應該先獲取上次存儲到的扇區的LBA地址,從而獲得此次存儲的起始扇區地址。為了記錄每次存儲到的扇區的地址,將LBA地址為0的扇區保留,專用于記錄扇區地址。在開始一次寫操作之前,應該先讀取LBA地址為O的扇區,獲得上次存儲的LBA地址;然后加1獲得此次寫操作的LBA地址,并向指定的扇區寫數據。

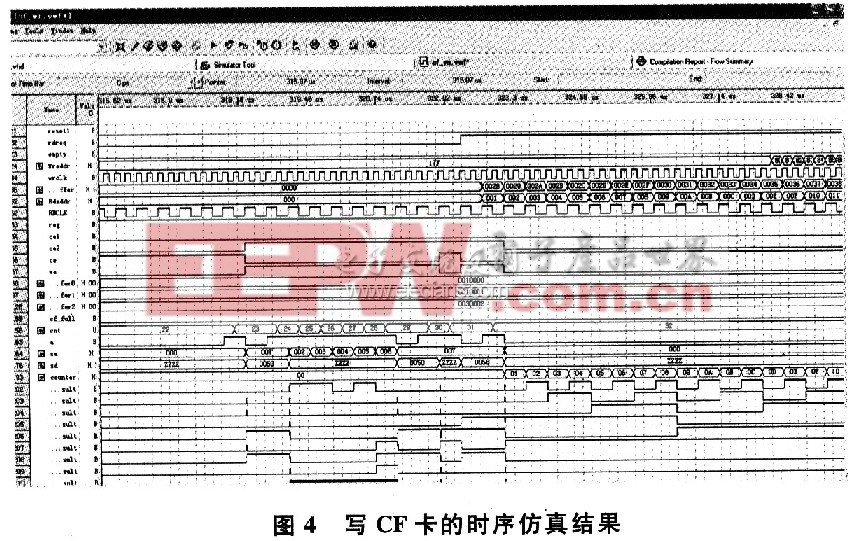

利用QuartusII作為FPGA開發平臺,使用VHDL硬件描述語言實現了FPGA與DSP的接口、異步FIFO的存儲以及CF卡的讀寫邏輯。在QuartusII自帶仿真工具下得到的寫CF卡時序仿真結果如圖4所示。

評論