直接擴頻通信同步系統的FPGA設計與實現

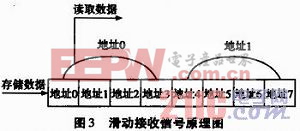

2.1 信號存儲器

信號存儲單元由一個雙口RAM構成,在采樣時鐘驅動下,接收信號按地址順序存于RAM中。RAM的讀取時鐘是做乘法的計算時鐘,在采樣速率不是很快時,計算時鐘可以是采樣時鐘的數十倍,可以達到上百兆,而讀取數據寬度也可以擴展為接收數據寬度的整數倍,一次讀取多個接收數據參與運算,這樣串行運算變為并行運算,極大提高了處理速度。如圖3所示,接收到的數據按從地址0到地址7的順序存儲,讀取數據寬度是接收信號的4倍,那么每存儲4個數據后讀取地址滑動一次,一次并行讀取4個數據和本地PN碼做乘法。本文引用地址:http://www.104case.com/article/155105.htm

如果PN碼周期是127,讀取寬度為40,那么4個計算時鐘就可以完成乘法計算,但是讀取寬度太寬會增加FPGA內部邏輯單元的使用量,需要在資源和速率方面做權衡。

2.2 PN碼存儲器

在傳統的滑動相關法中,PN碼如果選取m序列可由FPGA做反饋移位產生,順序讀取,這樣會影響運算效率。本文將PN碼由Matlab工具軟件生成,然后按一定格式存儲于FPGA內部存儲器,可選取ROM存儲,讀取寬度和信號存儲器的讀取寬度相同。PN碼存儲器不滑動,每次都按地址遞增順序讀取數據,操作和信號存儲器類似,不再贅述。

2.3 乘法器和積分器

這兩個模塊主要是實現接收數據和本地PN碼進行相關累加功能。接收到的數據首先和本地碼相乘,然后將相乘結果累加完成積分功能。

乘法并不需要FPGA器件內部的硬件乘法器,如果PN碼為1則將接收數據取正號,PN碼為0則將接收數據取負號。每個乘法器時鐘完成一個讀取地址中一組數據的乘操作,乘完將一組相乘結果求和后輸入到積分器進行每一組數據的累加。如果每組參與乘加的數據很多,一個時鐘不能完成加法運算可以采用流水線方法優化算法。

積分器累加的次數由PN碼長度和每次參與乘法運算的數據個數有關(即讀取數據的寬度),數據個數越多需要累加的次數越少。累加結束后將計算結果輸入到門限鑒別器做后續判決,同時積分器清零。

2.4 門限鑒別器

門限鑒別器的功能是對判決積分器的計算結果進行最大值檢測。檢測值超過門限預設值,則給跟蹤單元使能信號,啟動跟蹤功能,否則不作任何操作。

門限值的設定需要通過Matlab工具軟件仿真得出。m序列有很好的相關特性,當接收信號與本地碼同步時積分器會輸出一個明顯高于不同步時的峰值,在實際應用的場合由于噪聲大小不同峰值也不是固定值,要根據情況進行仿真設定一個比較適合的數值。數值過大會出現漏警現象,即已經同步但受噪聲影響積分器輸出值小于門限值而使系統無法正常工作。數值過小會導致不同步時啟動跟蹤單元。一般多次仿真,并把門限值設置稍大有利于系統正常運行。

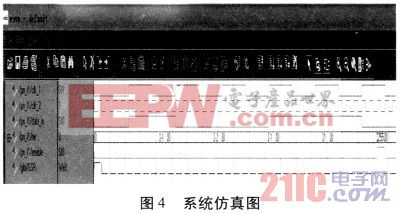

3 FPGA仿真結果與分析

本系統設計時選取的是Xilinx公司Virtex系列的XC4VSX35芯片,該芯片含有34560個邏輯單元,可用I/O腳448個,192個18×18 Xtreme DSP,18kb Block RAM 192個,最高工作頻率500M。以Xillnx公司的ISE 10.1開發軟件為平臺,運用Verlog語言作為輸入,并編譯、仿真、下載驗證了同步捕獲系統。圖4為系統仿真圖,clk_1是數據采樣時鐘,每次時鐘上升沿接收數據由data_in輸入,clk_2為計算時鐘,每次采樣一個數據后4個計算時鐘相關值由he輸出,由圖可以看出并行相關運算速度很快。本系統的門限值設置為125,如圖he值沒有超過門限值則下一個時鐘清零,如果系統捕獲成功he超過門限則輸入給跟蹤單元的使能信號enable保持一個周期的高電平,從而啟動跟蹤單元工作。

4 結論

本文提出的改進滑動相關算法運算速度快,捕獲時間短,實現起來比較簡單。利用FPGA設計并實現了算法,仿真結果滿足系統要求,該方法成功應用在擴頻通信解擴端,使用效果良好。

評論