基于SOPC的腦電信號實時處理

N是傅里葉變換的點數,此處為1 024點。

3)由于只計算相對功率,故在計算功率時沒有除點數N;

4)本計算的步長取1 ms,將與采樣頻率對應,給計算帶來方便。

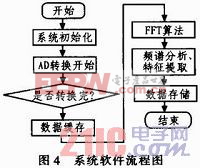

系統軟件流程圖如圖4所示。本文引用地址:http://www.104case.com/article/154471.htm

4 實驗結果

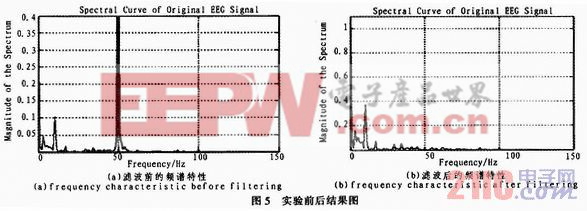

腦電信號是一種低頻且極其微弱的信號,一般為5~1 000μV。腦電信號的采集又常常伴隨著很大的噪聲干擾,尤其是50 Hz的工頻干擾。實驗結果如圖5所示。

經實驗結果分析,本設計可以有效完成對腦電信號的去噪及濾除50 Hz的工頻干擾,并能精確提取腦電信號的特征,為腦電信號的進一步研究做準備。

5 結束語

本設計的硬件實現都是在SOPC Builder環境下完成的,SOPC Builder提供的圖形化系統架構平臺極為方便地給設計人員提供了系統構建的優越性。SOPC Builder采用軟件搭建硬件系統的方法,突破了硬件系統難裁剪,不易升級,開發周期長,維護困難等諸多缺陷。而且SOPC Builder可根據搭建的硬件系統自動生成對應的代碼,可使各部件通過Avalon總線有序的連接和工作,將設計人員解放到系統框架的總體設計和用戶程序的設計,大大地促進了開發效率,縮短了開發流程。此外SOPC中也極為方便的為設計人員提供了加入自己設計的組建和自己定制的指令的功能,這樣可使開發人員可以通過自己定制的指令更加高效地完成設計。SOPC系統具有在硬件的可重構與可重配置,這是FPGA在硬件開發過程中獨一無二的特點。

評論