基于CBOC信號的導航接收機設計與實現

3 CBOC信號導航接收機設計實現

3.1 導航接收機硬件平臺

實現基于多相關器方法的接收機硬件平臺如圖4所示,硬件平臺選用FPGA作為實現相關器的模塊,利用FPGA的可編程特性,可以不改變硬件平臺,而只修改FPGA和DSP軟件實現對不同衛星導航系統的兼容接收。同時,FPGA的并行運算能力也能夠很好地保證基帶處理方法的實時性。

3.2 信號捕獲

由于CBOC信號中存在副載波,CBOC信號的相關函數存在±1碼片內存在多個相關峰值,為避免誤判,使用SCC(Sub—Carrier Cancellat ion)方法構造無模糊的相關函數,相關函數的計算方法如式(6)所示。

該方法有效地消除了CBOC信號的副峰,從而將CBOC信號的捕獲過程轉化成類似于BPSK信號的無模糊形式。

3.3 信號跟蹤

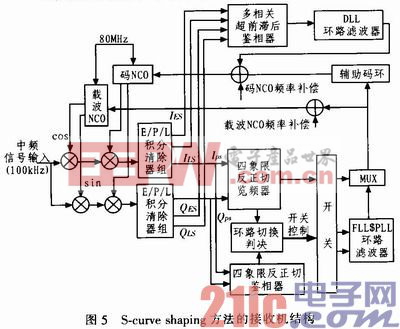

環路設計方案如圖5所示。本文引用地址:http://www.104case.com/article/153730.htm

跟蹤采用雙環路的策略,載波環和碼環。由載波發生器,載波鑒相器,碼發生器,碼鑒別器和相關器組等構成。CBOC信號的跟蹤采用多相關器的方式,只復制BOC(1,1)信號,然后根據計算的加權系數確定采用的鑒相方法。因此在硬件的設計中,碼環鑒別器的參數和鑒相方式均留出接口利用DSP或者ARM軟件配置。在確定了一組環路鑒相參數后,根據具體的應用場景,對環路參數進行微調。

載波跟蹤環路可以使用鎖頻環或者鎖相環完成對載波相位和頻率的跟蹤。在采用方多相關器方法的接收機中,繼承了BPSK接收機對載波跟蹤環的跟蹤方法,可以使用所有適用于BPSK接收機的鑒別器,在工程樣機的實現中使用了三階鎖相環,鑒相采用四象限反正切的方式,三階鎖相環的實現在這里不做討論。

3.4 接收機測試結果

在性能分析和算法仿真的基礎上,使用FPGA和DSP處理器的基帶處理架構實現S—SUrve shaping方法,經過對接Galileo信號模擬器,完成了對S—surve shaping方法的功能驗證,實現的跟蹤環路可以穩定地完成對載波、副載波和碼相位的跟蹤。

4 結論

文中通過分析CBOC的時域特性,自相關特性以及功率譜密度函數,主要論述了一種基于S—surve shaping跟蹤方法的Galieo E1頻點CBOC信號接收機的工程實現,在明確CBOC信號結構的情況下,充分利用Galileo信號在系統設計上的兼容性以及成熟的硬件平臺,并分析了使用簡化的CBOC信號接收方法所帶來的性能損失,在理論仿真的基礎上,完成了接收機的工程實現,實際運行的結果驗證了該方法的可行性。

評論