嵌入式SATA存儲系統的研究

SATA硬盤作為新型的存儲介質,具有高速、海量、價格低廉、使用方便等優點。SATA2.5協議支持3.0Gb/s的接口速度,SATA2.5硬盤的持續存儲速度可達80MB/s,最大存儲容量已經達到750GB(如希捷ST3750640AS硬盤)。SATA硬盤已經占據了大部分的PC機硬盤市場,并且正向工作站、服務器的領域邁進。而在嵌入式的應用領域,目前的硬盤存儲設備依然廣泛采用傳統的IDE(ATA)和SCSI硬盤。由于兩者存在低速或昂貴的缺點,因此如何將SATA硬盤存儲應用到嵌入式系統中就成為今后相關領域的研究重點。

1 SATA2.5協議的性能與結構

1.1 各種硬盤存儲接口的比較

通常硬盤根據接口類型進行分類。硬盤接口主要分為:IDE(ATA)、Serial ATA(SATA)、SCSI、Serial Attached SCSI(SAS)和Fiber Channel(FC),此外還存在IEEE1394、USB等。

IDE、SCSI采用的是并行總線接口,隨著技術要求的不斷提高,并行技術的種種問題如信號扭曲和串擾、電纜和連接器的反射、設備的尋址能力有限等都已成為提高其數據吞吐能力的障礙。FC、SAS和SATA采用串行技術,克服了并行技術存在的缺點,大大提高了速度、可靠性和可擴展性。而SATA硬盤相對于FC和SAS硬盤具有很大的價格優勢,并且與SAS接口兼容。

1.2 SATA2.5協議的基本性能[1]

SATA2.5是國際串行ATA組織SATA-IO(Serial ATA International Organization)制訂的最新SATA標準。其主要性能特點如下:

(1)傳輸速率快,由SATA1.0的1.5Gb/s發展到SATA2.5的3.0Gb/s,并且SATA-IO計劃今后幾年推出6.0Gb/s的接口協議,這比最新的并行IDE接口ATAPI-7的133MB/s的傳輸速率提高許多。

(2)電纜線寬度降低而長度增加,寬度由IDE的40針/80針減少到7針,長度由18英寸增加到1米。

(3)支持熱插拔,這使SATA硬盤可以作為移動硬盤使用。

(4)提高了數據傳輸的精確度,ATA-3標準引入了基于CRC(循環冗余碼校驗)的數據包出錯檢測,但是,沒有任何一種并行ATA標準提供命令和狀態包的出錯檢測。SATA提高了CRC對數據、命令和狀態包錯誤的檢測能力,從而提高了數據傳輸的精確度。

(5)支持全速命令隊列(NQC),大大提高了硬盤的內部數據傳輸速度。

此外,SATA2.5協議采用點對點結構,降低了磁盤陣列的出錯風險;降低了工作電壓,減少了功耗;向下軟件兼容并行ATA,橫向兼容SAS協議。

1.3 SATA2.5協議的體系結構

SATA2.5采用四層結構:應用層、傳輸層、鏈接層和物理層。其中,應用層負責所有ATA命令的執行,包括對控制命令模塊寄存器的訪問;傳輸層負責在主機和硬盤設備之間以幀信息結構(FIS)的形式傳輸控制命令和數據;鏈接層負責對數據進行8/10編解碼,根據需要從結構幀中提取有效數據,或者將控制字插入到結構幀當中;物理層負責在串行數據線上傳輸已編碼的數據。

2 Virtex-5 FPGA芯片簡介[2]

Virtex-5系列FPGA芯片[2]是Xilinx公司最新推出的高端產品,它采用65納米工藝,1.0V核電壓,具有靈活的時鐘管理模塊,100Mb/s~3.2Gb/s的串行連接功能,550MHz的DSP硬核,內置36KB的塊RAM, I/O引腳多達1 200個。目前,Virtex5系列FPGA有LX、LXT和SXT三款平臺,分別面向高性能邏輯功能、高性能邏輯功能和高速串行連接,以及高速串行連接和DSP功能。

RocketIO GTP收發器是專門為Virtex-5 FPGA實現高速低功耗串行連接而設計的,具有高速、穩定的特點,可以實現PCI Express、FC、SATA等高速接口的物理層協議,而不用外置子板,從而節省了空間和成本。

3 SATA2.5協議在FPGA上的實現[3][4]

3.1 鏈接層在FPGA內的實現

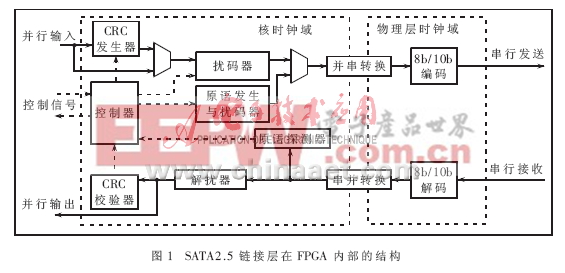

鏈接層發送或者接收混合了控制原語的數據流,在數據傳輸過程中,CRC被加入或者提取出數據流,同時8b/10b編解碼被執行。圖1給出了鏈接層在FPGA內部的邏輯結構,左邊與傳輸層相連,右邊與物理層相連。

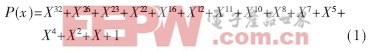

在核時鐘域里,數據寬度是32位;而在PHY時鐘域里,數據寬度是10位。在發送過程中,異步接口每四個PHY時鐘發送一次雙字,每個PHY時鐘內一個8位數據塊通過8b/10b編碼器生成10位數據塊,并被連續串行發送到物理層。接收過程剛好與此相反。原語是由雙字組成的實體,用于控制和提供串行連接的狀態。在FPGA內部,原語專門由原語發生器提供,主控制器根據上層命令控制原語的產生。CRC發生器多項式為:

評論