基于DSP和SOPC數字信號發生器的設計

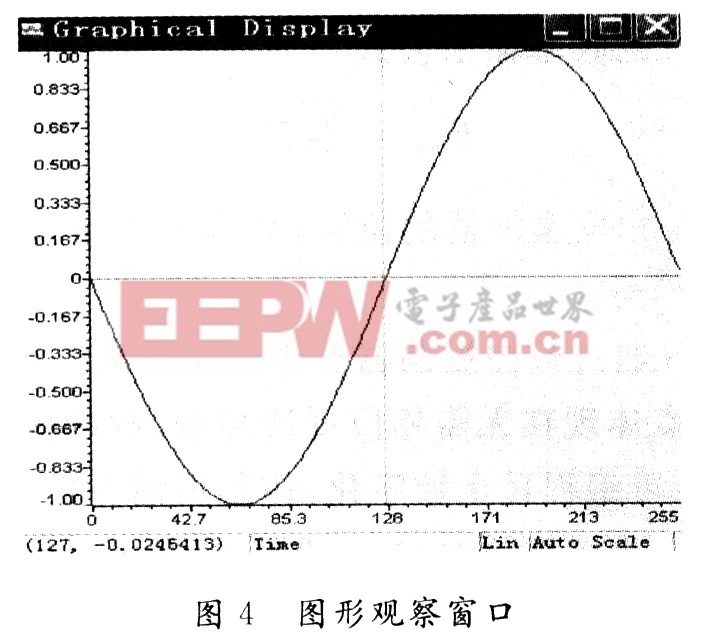

輸出結果顯示,在CCS圖形觀察窗口得到了頻率穩定,信號干擾小,波形失真度較小的正弦信號;利用示波器也可觀察到波形較好,穩定的正弦信號。

2 基于SOPC技術設計正弦信號發生器

盡管DSP處理器(如TI的TMS320系列)在過去很長一段時間幾乎是DSP應用系統核心器件的惟一選擇。但由于其自身的局限性,例如不靈活的硬件結構,使得其很難滿足當今迅速發展的DSP應用市場。現代大容量、高速度、內嵌有各種DSP模塊的FPGA和相應的SOPC技術出現,使得數字信號處理的實現更加容易。

2.1 DDFS原理

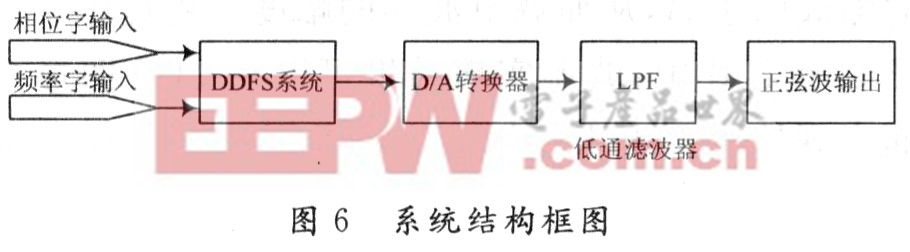

直接數字頻率合成(DDFS)電路由系統時鐘、相位累加器、頻率累加器、波形查找表、D/A轉換器和信號調理電路構成。DDFS的工作原理是在每個時鐘周期,用頻率累加器以輸入頻率字FW為步進進行自增累加,累加結果的高位送相位累加器,并與輸入的相位字PW進行累加,相位累加的輸出作為波形查找表的地址,從查找表中讀出相應的數據送給D/A轉換器,最后經過低通濾波器、后級放大等信號調理電路,以形成模擬量波形輸出。圖6給出系統結構框圖。

DDFS的頻率輸出公式:

式中:N為相位累加器的位寬;M為頻率字位寬;Fclk為系統時鐘信號。

DDFS通過數控振蕩器產生頻率、相位可控的正弦波。其優點體現在無需相位反饋控制,頻率建立及頻率切換較快,可編程且全數字化,控制靈活方便,輸出相位連續。如果在相位累加器的位數N足夠大時,理論上可以獲得很高的分辨精度,應用DDFS還可以產生其他多種調制信號,因此具有極高的性價比。

2.2 硬件模塊設計與仿真

利用DSP BuiIder進行DSP模塊設計是SOPC技術的一個組成部分。關鍵設計過程在Matlab的圖形仿真環境Simulink中進行,用圖形方式調用DSP Builder和其他Simulink庫中,圖形模塊,構成系統級設計模塊,如圖7所示。

評論