基于DSP和SOPC數(shù)字信號(hào)發(fā)生器的設(shè)計(jì)

1.2 硬件設(shè)計(jì)

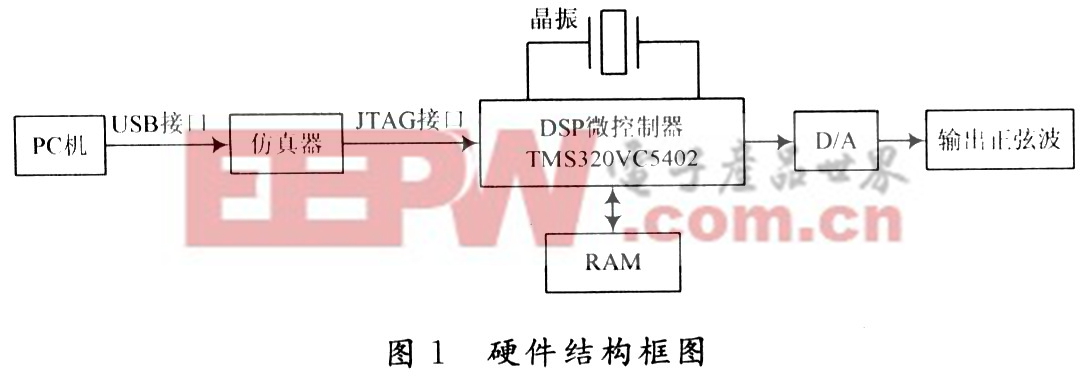

系統(tǒng)硬件主要由微機(jī)、DSP芯片、數(shù)/模轉(zhuǎn)換模塊組成。其中,DSP芯片采用的是TI公司性價(jià)比良好的TMS320VC5402。它有一組程序總線和三組數(shù)據(jù)總線、高度并行性的算術(shù)邏輯單元ALU、專用硬件邏輯片內(nèi)存儲(chǔ)器、增強(qiáng)型HPI口和高達(dá)100 MHz的CPU頻率。它可以在一個(gè)周期里完成兩個(gè)讀和一個(gè)寫操作,并且具有專門的硬件乘法器,廣泛采用流水線操作,提供特殊的DSP指令,可以用來快速地實(shí)現(xiàn)各種數(shù)字信號(hào)處理算法。D/A采用了一種雙極型8位、低功耗數(shù)/模轉(zhuǎn)換器DAC08,實(shí)現(xiàn)了高速同步數(shù)/模轉(zhuǎn)換。硬件結(jié)構(gòu)框圖如圖1所示。本文引用地址:http://www.104case.com/article/152419.htm

1.3 軟件設(shè)計(jì)

軟件設(shè)計(jì)是基于CCS開發(fā)環(huán)境的。CCS是TI公司推出的為開發(fā)TMS320系列DSP軟件的集成開發(fā)環(huán)境,是目前使用最為廣泛的DSP開發(fā)軟件之一。它提供了環(huán)境配置、源文件編譯、編譯連接、程序調(diào)試、跟蹤分析等環(huán)節(jié),并把軟、硬件開發(fā)工具集成在一起,使程序的編寫、匯編、程序的軟硬件仿真和調(diào)試等開發(fā)工作在統(tǒng)一的環(huán)境中進(jìn)行,從而加速軟件開發(fā)進(jìn)程。本文采用了與硬件開發(fā)板相結(jié)合的在線編程模式,通過CCS軟件平臺(tái)上應(yīng)用C語言及C54X匯編語言來實(shí)現(xiàn)正弦信號(hào)發(fā)生裝置。

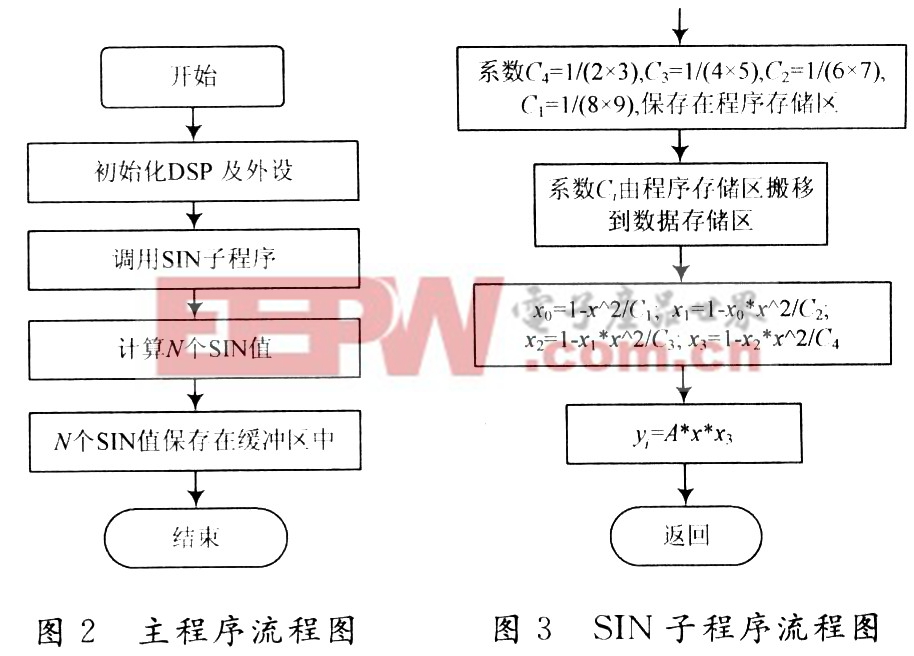

軟件設(shè)計(jì)的思想是:正弦波的波形可以看作由無數(shù)點(diǎn)組成,這些點(diǎn)與x軸的每一個(gè)角度值相對(duì)應(yīng),可以利用DSP處理器處理大量重復(fù)計(jì)算的優(yōu)勢(shì)來計(jì)算x軸每一點(diǎn)對(duì)應(yīng)的y的值(在x軸取N個(gè)點(diǎn)進(jìn)行逼近)。整個(gè)系統(tǒng)軟件由主程序和基于泰勒展開法的SIN子程序組成,相應(yīng)的軟件流程圖如圖2和圖3所示。

程序中,N值為產(chǎn)生正弦信號(hào)一個(gè)周期的點(diǎn)數(shù),產(chǎn)生的正弦信號(hào)頻率與N數(shù)值大小及D/A轉(zhuǎn)換頻率fDA有關(guān),產(chǎn)生正弦波信號(hào)頻率f的計(jì)算公式為:

f=fDA/N

因此,選擇每個(gè)正弦周期中的樣點(diǎn)數(shù),改變每個(gè)采樣點(diǎn)之間的延遲,即通過調(diào)節(jié)N值產(chǎn)生不同頻率的波形,同時(shí)也可以利用軟件改變輸出的離散波形值乘以相應(yīng)的縮放因子A,從而調(diào)節(jié)波形的幅度。將程序裝載到DSP目標(biāo)芯片中,波形實(shí)現(xiàn)結(jié)果可以在CCS圖形顯示界面直觀地表示出來(見圖4)或者用示波器觀察輸出結(jié)果如圖5所示。

評(píng)論