基于FPGA/CPLD的嵌入式VGA顯示系統

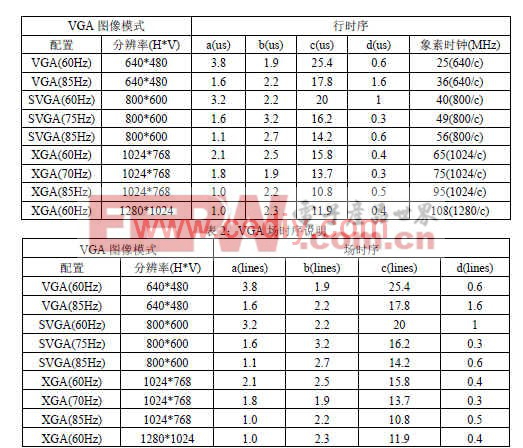

幾種常用的時序參數如表 1和表2 所示,首先,根據顯示器的性能選擇一種合適的VGA模式,然后由象素時鐘頻率和圖像分辨率計算出行總周期數,再把表 1和表 2中給出的 a、 b、c、d各時序段的時間按照象素計數脈沖源頻率折算成時鐘周期數。在 FPGA/CPLD中用計數器和觸發器,以計算出的各時序段時鐘周期數為基準,產生不同寬度和周期的脈沖信號,再利用它們的邏輯組合構成圖 2和圖 3中的 a、b、c、d各時序段以及 ADV7125的空白信號 BLANK和同步信號 SYNC。

一個示例就是 60Hz時 1280×1024分辨率顯示的 VESA標準,在 60Hz時,屏幕每

16.67毫秒更新一次。這個標準制定了幀大小,用它來定義分辨率和回掃次數之間的關系。對于分辨率大小為 1280×1024來說,幀的大小為 1688×1066,這個大小與像素時鐘(Pixel Clock)有關,所謂像素時鐘就是對像素的刷新頻率。像素時鐘為 1688×1066×60Hz 或者 108 兆 Hz(MHz)時,每個像素的刷新頻率也就是大約 9.26納秒,那么行頻就為 60×1066=63960 行/秒,也就是用顯示器的幀率乘以掃描線數量。可以用幀大小得到縱向回掃次數,為了得到縱向同步長度(Sync Length),可以從縱向幀大小減去縱向分辨率,也就是 1066-1024=42。這樣,縱向回掃花費的時間和在屏幕上繪出 42 條線的時間相同,對于縱向回掃來說需要的時間為 42×1688×9.26 納秒(656 微秒)。

在顯示時序段( Display interval c),數據讀寫控制器從數據緩存區讀取像素顏色,用這些顏色來控制輸出設備(顯示器)的亮度。一幀圖像就準確的顯示到 VGA顯示器上。

表 1:VGA行時序說明

評論