一種靈活的包含嵌入式存儲(chǔ)器的FPGA結(jié)構(gòu)

3.1結(jié)構(gòu)描述

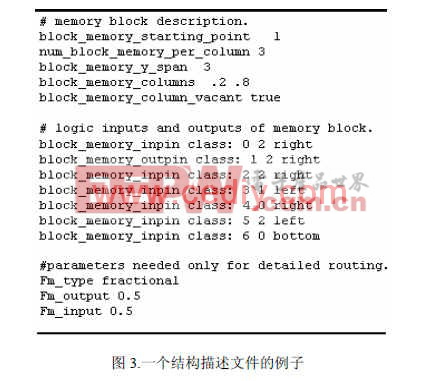

VPR用布線結(jié)構(gòu)描述語(yǔ)言定義 FPGA的布線結(jié)構(gòu)【 5】。VPR通過(guò)一個(gè)內(nèi)部的“結(jié)構(gòu)產(chǎn)生器”來(lái)產(chǎn)生 RRG。我們擴(kuò)展了布線結(jié)構(gòu)描述語(yǔ)言來(lái)定義包含嵌入式存儲(chǔ)器的 FPGA的布線結(jié)構(gòu),然后我們改進(jìn)了 VPR的結(jié)構(gòu)產(chǎn)生器以適應(yīng)這些擴(kuò)展。

由于嵌入式存儲(chǔ)器模塊的存在,我們對(duì)布線結(jié)構(gòu)描述語(yǔ)言的擴(kuò)展主要包括:(1)存儲(chǔ)器模塊的列數(shù),(2)每列存儲(chǔ)器模塊的相對(duì)位置,(3)存儲(chǔ)器模塊輸入和輸出引腳的 Fm值,(4)每列存儲(chǔ)器模塊中的存儲(chǔ)器模塊數(shù)目,(5)每列存儲(chǔ)器模塊中第一個(gè)存儲(chǔ)器模塊的起始位置,

(6)存儲(chǔ)器模塊的高度,(7)存儲(chǔ)器模塊輸入輸出引腳的數(shù)目,(8)存儲(chǔ)器模塊每個(gè)輸入或輸出引腳對(duì)應(yīng)的邊( side)和群( cluster),例如如圖 2所示的 FPGA結(jié)構(gòu)中,存儲(chǔ)器模塊的左邊和右邊共有 3個(gè)群,因?yàn)榇鎯?chǔ)器模塊的高度是 3個(gè)邏輯模塊的高度,而上下兩邊只有一個(gè)群。(9)每個(gè)存儲(chǔ)器模塊中的組合邏輯電路延遲和時(shí)序電路延時(shí)。本文引用地址:http://www.104case.com/article/152390.htm

圖 3所示為一個(gè)描述包含嵌入式存儲(chǔ)器的 FPGA布線結(jié)構(gòu)的文件的一部分,其中邏輯模塊由一個(gè) 4輸入的查找表和一個(gè)寄存器構(gòu)成。圖 1和圖 2示出了這種 FPGA的結(jié)構(gòu)。VA產(chǎn)生的文件要滿(mǎn)足圖 3定義的結(jié)構(gòu),其中需要的布線通道寬度為 5,即 5條連線。這些描述 FPGA結(jié)構(gòu)的圖形都是由我們的 VA產(chǎn)生。圖 1示出了整個(gè) FPGA的結(jié)構(gòu),這種情況下,整個(gè) FPGA包含 9x9個(gè)邏輯模塊,周?chē)鷩@ I/O模塊。黃色所示的為兩列存儲(chǔ)器模塊,每個(gè)存儲(chǔ)器模塊跨越 3個(gè)邏輯模塊的高度。圖 2所示僅為 FPGA近距離結(jié)構(gòu)的一部分,這樣我們能清楚的看到布線結(jié)構(gòu)。黑色線表示布線資源,小的藍(lán)紅色矩形分別表示模塊的輸入和輸出引腳,綠色的連線代表連接開(kāi)關(guān)。

3.2布線資源圖

雖然上述所列的結(jié)構(gòu)參數(shù)使得 FPGA的結(jié)構(gòu)很容易就可以定義,但是對(duì)于布線器來(lái)說(shuō)它并不是一個(gè)合適的表達(dá)方法。在 RRG中,連線、邏輯模塊的引腳以及存儲(chǔ)器模塊的引腳都被表示為節(jié)點(diǎn),開(kāi)關(guān)被表示為連接兩個(gè)節(jié)點(diǎn)的邊。

如前所述,我們對(duì) VPR的結(jié)構(gòu)產(chǎn)生器作了改進(jìn)以建立包含嵌入式存儲(chǔ)器的 FPGA的 RRG。由于存儲(chǔ)器模塊在 Y方向跨越多個(gè)邏輯模塊,這就使得在 RRG中插入存儲(chǔ)器模塊的引腳變得復(fù)雜,同時(shí)連接從存儲(chǔ)器模塊輸出引腳到連線以及從連線到存儲(chǔ)器輸入引腳的邊也更加復(fù)雜。但幸運(yùn)的是如圖 2所示,存儲(chǔ)器模塊的存在并不破壞布線通道的分布。為了方便建立 RRG,我們?cè)黾恿颂摌?gòu)存儲(chǔ)器模塊的定義,在建立 RRG的過(guò)程中,存儲(chǔ)器模塊的位置由它的起始位置來(lái)表示。剩余的其它被占領(lǐng)的邏輯塊位置被分配給虛構(gòu)存儲(chǔ)器模塊。當(dāng)在建立 RRG對(duì)所有模塊進(jìn)行掃描的時(shí)候,我們對(duì)存儲(chǔ)器模塊以及虛構(gòu)存儲(chǔ)器模塊的處理方法和對(duì)邏輯塊的處理方法是一樣的。通過(guò)這樣的方法,我們簡(jiǎn)化了創(chuàng)建異質(zhì) FPGA布線資源圖的過(guò)程。

4.結(jié)論

本文中,我們提出了一種包含嵌入式存儲(chǔ)器的 FPGA的靈活結(jié)構(gòu)以及一種建立 RRG的簡(jiǎn)化方法。我們對(duì) VPR進(jìn)行了改進(jìn),擴(kuò)展了其功能,使得它可以處理包含嵌入式存儲(chǔ)器的 FPGA結(jié)構(gòu),同時(shí)保持了原有的靈活性。而 VPR原有的布局布線算法完全適用于我們的 FPGA結(jié)構(gòu)。我們繼承 VPR的方法來(lái)描述包含嵌入式存儲(chǔ)器的 FPGA結(jié)構(gòu),并且擴(kuò)充了 VPR的自動(dòng)結(jié)構(gòu)描述器功能。

縱觀整個(gè)工作,我們著重處理包含嵌入式存儲(chǔ)器模塊的 FPGA結(jié)構(gòu),我們假設(shè)存儲(chǔ)器模塊按列排放。我們的這種結(jié)構(gòu)不僅適用于存儲(chǔ)器模塊,同時(shí)也適用于其他的按列排放的功能模塊,例如 Spartan-3系列 FPGA中的乘法器模塊以及 Stratix系列 FPGA中的 DSP模塊。

本文作者創(chuàng)新觀點(diǎn):本文中,我們提出了一種靈活的包含嵌入式存儲(chǔ)器的 FPGA結(jié)構(gòu)以及一種建立 RRG的簡(jiǎn)化方法。我們對(duì) VPR進(jìn)行了改進(jìn),擴(kuò)展了其功能,使得它可以處理包含嵌入式存儲(chǔ)器的 FPGA結(jié)構(gòu),同時(shí)保持了原有的靈活性。

評(píng)論