基于DSP Builder的腦電信號(hào)小波處理

設(shè)信號(hào)為:本文引用地址:http://www.104case.com/article/152315.htm

由于φ(-t)和φ(t-s)為構(gòu)造正交小波的多分辨率分析尺度函數(shù),因此上述分解和重構(gòu)公式中取h(n)為h(-n)或h(n-s)均可。為了討論方便,且不失一般性,可將上述分解公式和重構(gòu)公式重寫(xiě)為:

帶入式(9)得:

則c0(k)=c0(k-2N-1),式(13)得到的信號(hào)是式(12)得到信號(hào)的延遲。由于序列h(n)和g(n)為因果序列,所以式(13)對(duì)應(yīng)的濾波器為因果濾波器。采用式(7)和式(8)繼續(xù)分解信號(hào)低頻分量或低頻分量與高頻分量.可得多級(jí)分解或小波包分解。

3 基于DSP Builder的小波變換設(shè)計(jì)實(shí)現(xiàn)

考慮到瞬態(tài)脈沖信號(hào)的短時(shí)性,選擇具有緊支集的Daubenchies小波作為分析小波,這樣有利于突出瞬態(tài)信號(hào)特征,DB小波函數(shù)具有良好的正交性和緊支撐性,可較好地表現(xiàn)頻域信號(hào)的連續(xù)性和突變性,在實(shí)際工程應(yīng)用中效果較好。故這里采用DB小波對(duì)腦電信號(hào)進(jìn)行4級(jí)分解重構(gòu)。濾除腦電信號(hào)中存在的直流成分或緩慢基線漂移。選取DB2小波,此時(shí)M=3,且低通濾波系數(shù)(尺度函數(shù)系數(shù))如下:

由于浮點(diǎn)數(shù)在FPGA中實(shí)現(xiàn)比較復(fù)雜,為了減少FPGA的運(yùn)算量和資源,可將濾波計(jì)算轉(zhuǎn)換為整數(shù)運(yùn)算和移位運(yùn)算,為此首先需將以上濾波器系數(shù)轉(zhuǎn)化為整數(shù),對(duì)每個(gè)濾波器系數(shù)采用16位字長(zhǎng)進(jìn)行量化,即乘以215后取整數(shù),而對(duì)濾波器的輸出信號(hào)有移15位即得到實(shí)際輸出。

以DSP Builder為平臺(tái),對(duì)式(7)、式(8)和式(13)算法進(jìn)行系統(tǒng)級(jí)建模、仿真,再利用Signal Compiler生成HDL文件,然后利用Quartus II進(jìn)行時(shí)序仿真驗(yàn)證。

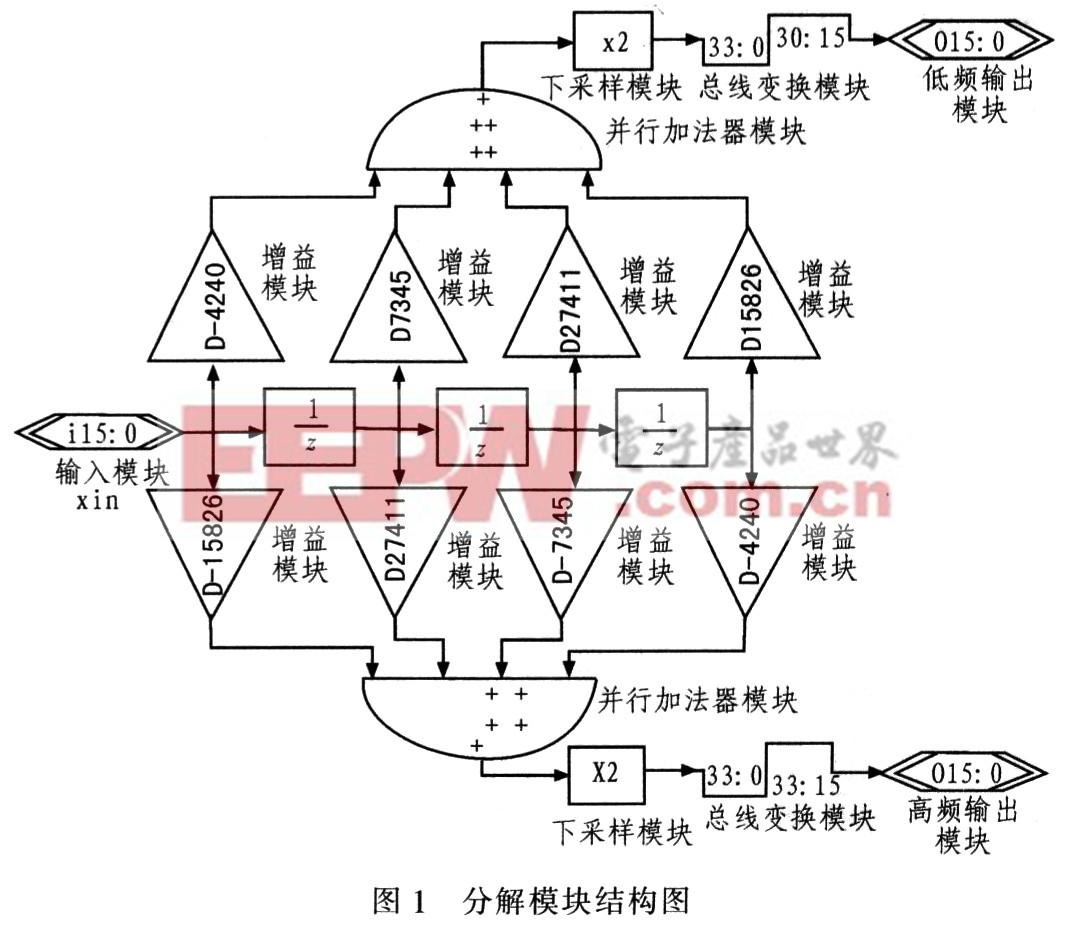

3.1 DSP Builder實(shí)現(xiàn)lD-DWT分解

分解模塊的結(jié)構(gòu)如圖1所示。信號(hào)并行從4級(jí)延遲線輸出,與FIR濾波器系數(shù)進(jìn)行卷積,然后再偶抽取便可得到近似部分和細(xì)節(jié)部分的結(jié)果。二次抽取模塊采用DSP Builder的下采樣模塊,利用Signal Compiler生成HDL文件。

為了減少系統(tǒng)耗用的硬件資源,舍去輸出結(jié)果的低8位,保證分解前后信號(hào)保持同樣能量級(jí)。從圖1中可知,各個(gè)子模塊并行工作,子模塊之間無(wú)需任何交叉信號(hào),數(shù)據(jù)從輸入端以流水線的方式向后傳遞,實(shí)現(xiàn)實(shí)時(shí)流水線工作。二級(jí)分解模塊的設(shè)計(jì)原理同一級(jí)分解模塊。

評(píng)論