基于FPDP的高速數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)

FPDP接收邏輯接收來自A/D板的回波數(shù)據(jù),主要負(fù)責(zé)對數(shù)據(jù)緩沖區(qū)FIFO的寫入操作。其工作流程如下:在FPDP總線數(shù)據(jù)有效(DVALIDn為低)時,F(xiàn)IFO的寫請求Wr-req信號有效,此時數(shù)據(jù)隨著寫時鐘信號(Wr-clk即AD板發(fā)送過來的Ad-strob信號)寫入FIFO。若FPDP總線數(shù)據(jù)無效,此時FIFO的寫請求信號也無效,數(shù)據(jù)不能寫入FIFO。

FPDP發(fā)送邏輯接負(fù)責(zé)將回波數(shù)據(jù)和其他飛機(jī)參數(shù)按照一定的格式打包,并經(jīng)由FPDP總線發(fā)送出去。其工作流程如下:FIFO的讀請求Rd-req信號由發(fā)送時序計(jì)數(shù)器產(chǎn)生,當(dāng)計(jì)數(shù)器的計(jì)數(shù)值為一定值(A/D采集滿一幀數(shù)據(jù))時,Rd-req有效,隨著讀時鐘(Rd-clk即A/D板時鐘AD_strob)信號,數(shù)據(jù)從FIFO中讀出,此時計(jì)數(shù)器清零。數(shù)據(jù)按一定格式打包后,按FPDP單幀傳輸模式將打包數(shù)據(jù)送入DSP板。

FPDP發(fā)送邏輯應(yīng)當(dāng)在FPDP同步信號SYNCn到來后立即啟動數(shù)據(jù)發(fā)送,這樣大大增強(qiáng)了數(shù)據(jù)傳輸?shù)膶?shí)時性和可靠性。值得注意的是,A/D板傳來的第一組回波數(shù)據(jù)來不及打包傳送給DSP板,因此要在FIFO中累積一組回波數(shù)據(jù)后再開始往DSP板發(fā)送數(shù)據(jù),這樣每次發(fā)給DSP板的一幀數(shù)據(jù)中,回波數(shù)據(jù)應(yīng)為上一次A/D板發(fā)來的數(shù)據(jù),這樣可以保證不丟失回波數(shù)據(jù),只是最后一組回波數(shù)據(jù)仍然會存在于時序板中,采集不到,應(yīng)當(dāng)丟棄。

特別地,由于模塊的輸入輸出功能已確定,所以作為A/D板接收端的方向信號DIRn不被使用,而作為DSP板發(fā)送端的DIRn信號則常接低。對于輸入的SUSPENDn和NRDYn信號,A/D采集板對NRDYn信號不響應(yīng),所以FPGA對這兩個信號也不響應(yīng),避免干擾AD采集板的數(shù)據(jù)采集。本文引用地址:http://www.104case.com/article/152271.htm

3 設(shè)計(jì)仿真

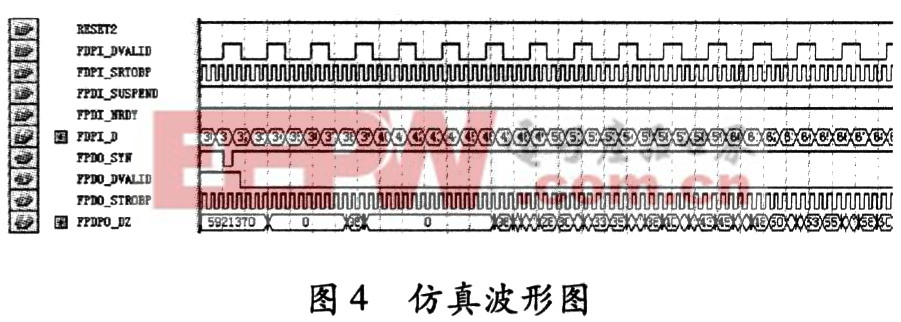

以下給出了基于Quartus 6.0的一段波形仿真圖,如圖4所示。

如圖4所示,為FPDP發(fā)送邏輯的仿真圖,其中FPDI_SUSPEND和FPDI_NRDY始終無效(為高),在發(fā)送數(shù)據(jù)前FPDO_SYN先有效(為低),此時FPDO_DVALID仍無效(為高)。在傳輸數(shù)據(jù)時,F(xiàn)PDO_DVALID有效(為低),在時鐘FPDO_STROBP的上升沿將數(shù)據(jù)通過FPDP總線送出。

4 結(jié)束語

從以上的分析得出以下結(jié)論:

(1)該設(shè)計(jì)中,F(xiàn)PDP總線以其特有的前面板方式和傳輸機(jī)制,有效地解決了多塊板卡間的高速數(shù)據(jù)傳輸問題;

(2)FPDP數(shù)據(jù)的高速、實(shí)時接收和發(fā)送是難點(diǎn)。該設(shè)計(jì)采用了一個片內(nèi)FIFO緩沖區(qū)解決了此問題。片內(nèi)FIFO集成度高、占用資源少,有效地解決了系統(tǒng)需求;

(3)該設(shè)計(jì)使用同步信號作為接收幀的有效標(biāo)志,提高了系統(tǒng)的實(shí)時性和可靠性。

評論