基于DSP+FPGA的實時視頻采集系統設計

0 引言

圖像是自然生物或人造物理的觀測系統對世界的記錄,是以物理為載體,以介質來記錄信息的一種形式。圖像信息是人類認識世界的重要知識來源。據學者統計,人類所得的信息有80%以上是來自眼睛攝取的圖像。而事實上,這種靜態的圖像已無法滿足人們對視頻信息的要求。隨著人們對視頻數據的要求越來越高,高清晰、實時性視頻數據量越來越大,視頻的實時處理難度也在逐漸增大。本文給出了一款基于DSP+FPGA的嵌入式實時視頻采集系統的設計方法,該系統可以廣泛應用于關系公共安全的場所,如銀行、機場、車站、商場等。

1 實時視頻采集系統結構

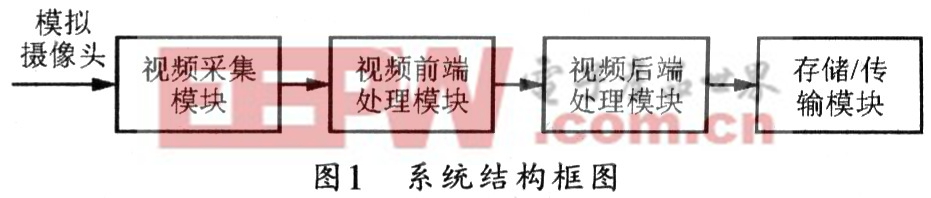

常見的視頻采集系統主要有兩種:一種是基于單處理器(單片機、ARM等)的視頻采集卡,特點是結構簡單,易于實現,缺點是無法實時地對視頻數據完成處理,需要使用外部處理器來完成特定的視頻處理算法,因而成本高,升級維護難度大;另一種是基于主從處理器(ARM+DSP,FPGA+DSP等)的嵌入式視頻采集卡,特點是系統高度集成,易于維護升級,可以滿足視頻采集的需求,同時可以完成特定的視頻算法,成本較低。因此,本文給出了一種基于DSP+FPGA的嵌入式視頻采集系統設計方案。其系統結構框圖如圖1所示。

2 系統硬件設計

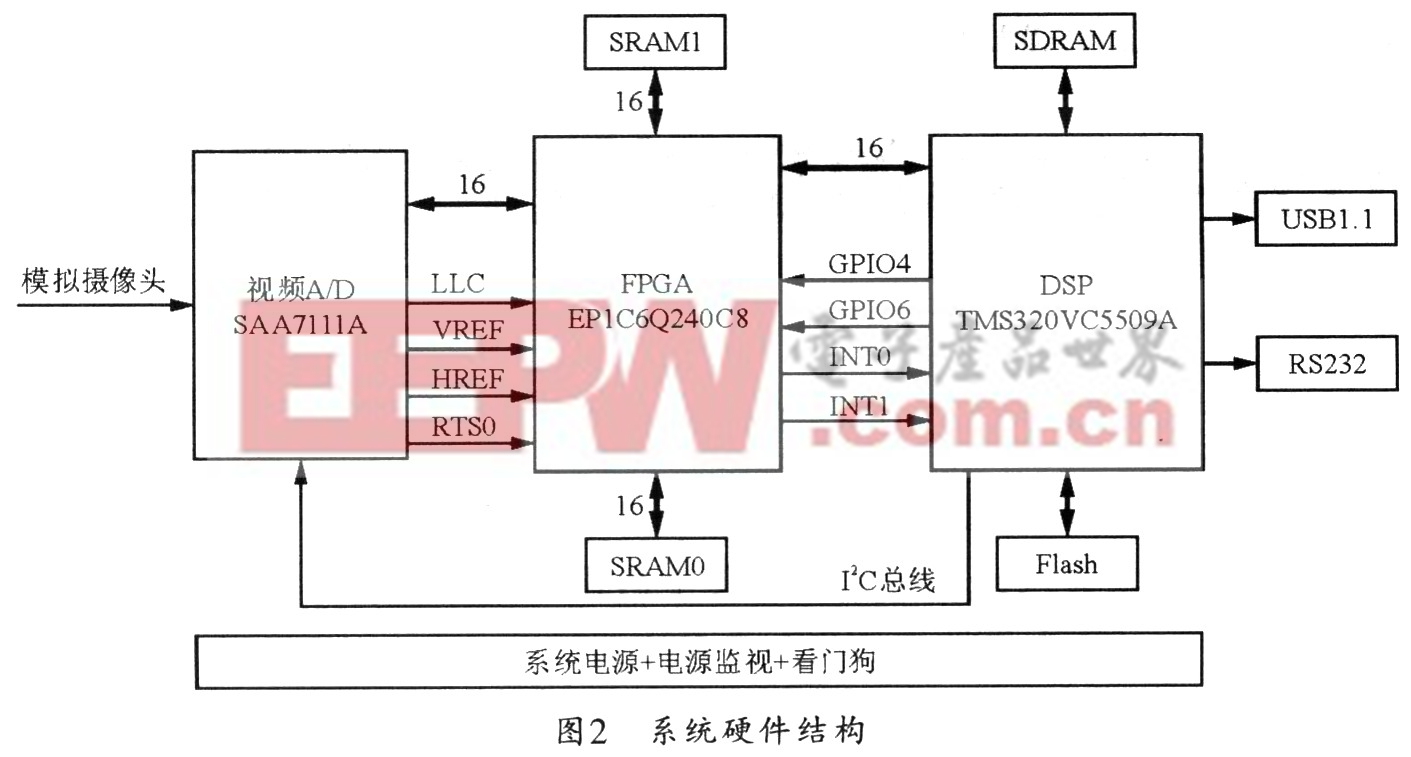

本系統的設計思路是通過模擬的視頻攝像頭來獲取視頻信號,然后采用模數轉換芯片SAA71 11A將模擬的PAL制式視頻信號轉換為YUV4:2:2的數字視頻信號。設計使用FPGA芯片EP1C6Q240C8作為協處理器,來完成視頻信號的緩存和視頻幀的合成,通過雙RAM的乒乓結構來實現視頻幀的完整性,并在完成視頻數據的預處理后,將視頻數據傳入到DSP中,完成特定的視頻處理算法(如壓縮等),最后對處理完的視頻數據進行傳輸和存儲。同時,主處理器DSP還負責對視頻采集芯片進行初始化配置。其系統硬件結構如圖2所示。

2.1 視頻采集模塊

設計一個視頻采集系統的重要環節,通常是將外部的光信號轉換成電信號,然后通過專用的視頻轉換芯片,來將模擬的視頻信號轉換為數字視頻信號。本設計采用的是模擬CMOS攝像頭和Philips公司的高性能視頻模數轉換集成電路芯片SAA71 11A。

評論