TMS320F206外圍電路典型設計

AD669數據鎖存采用分段譯碼結構(Segmented Decoded Architecture),可減少與數碼相關的毛刺,同時采用雙緩存鎖存結構,避免了虛假模擬信號的產生。AD669內部集成隱埋式齊納基準,10.000 V基準最大誤差為±0.2%。另外AD669具有管腳可定義單極(0~10 V)雙極性(一10~+l0 V)輸出,并可實現增益及零偏調節。

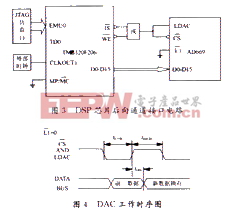

DSP芯片(TMS320F206)工作于20 MHz時鐘周期,外掛JTAG仿真口,便于實時燒寫、調試程序。DAC工作于邊沿觸發模式,即LDAC與CS連接在一起,而L1直接接地,兩級鎖存鏈接成主從結構。

TMS320F206與AD669接口電路框圖如圖3所示。

正常工作狀態下,當DSP的I/O口空間選擇信號IS以及寫選擇信號WE其中一個由低變高時,則會使D/A的LDAC-CS產生上升沿(tLOWtHIGH),開始同時更新兩級鎖存中的數據。其工作時序如圖4所示。

4 F206外部數據存儲器擴展

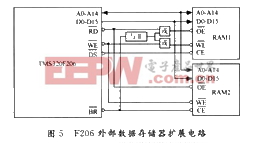

DSP芯片通常需要通過外部存儲器來擴展數據存儲空間。F206內部集成64 kB數據存儲空間,外部數據存儲器可以擴展至32 kB空間。為了使存儲接口速度快,選用ISSI公司的高速存儲器IS61C3216,該數據存儲器為32 k×16 b的CMOS靜態RAM,其讀寫訪問時間僅為10 ns。

F206芯片的總線請求信號BR以及全局存儲器分配寄存器GREG可以把數據存儲器擴展至32kB空間。用兩塊IS61C3216,一組作為局部數據存儲器,一組作為全局數據存儲器,地址共用8000h~FFFFh。其擴展電路框圖如圖5所示。

當GREG=xx00h時,8000h~FFFFh地址區域被配置為局部數據存儲器,此時,BR=1,RAM2禁止訪問,RAM1兩個使能信號打開,選中RAM1;當GREG=xx80h時,8000h~FFFFh被配置為全局數據存儲器,此時,BR=0,RAMl被禁止局部數據存儲器將不能訪問。

通過外部存儲器擴展,F206具有64kB的局部數據存儲器空間,用來存放指令使用的數據;32 kB的全局數據存儲器空間,用來存放與其他處理器共用的數據。

5 結 語

本文以TMS320F206為例詳細闡述了DSP芯片前向通道、后向通道接口電路的設計思路及方法。在系統資源受到限制或設計需要的情況下,可以將A/D和D/A同時配置在DSP的擴展總線上。此時,最重要的是綜合考慮A/D和D/A與DSP收發數據時序的匹配。本文設計方案,以電路板的方式已運用于廠家的產品中,對機載雷達的大規模、復雜性信號處理發揮了一定的作用。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論