直擴導航系統中數字科思塔斯環的FPGA設計與實現

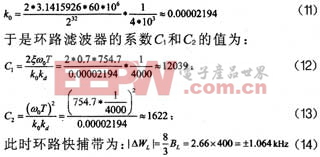

在用這組值完成頻率跟蹤后,取窄帶的環路濾波器進行相位鎖定。這時取B_{L}=0.01R_{b}=40H_{z},此時的計算結果為:C_{1}=1203.9;C_{2}=16.22;快捕帶為:106.4Hz。

總的來說,環路濾波器系數C_{1}和C_{2}需要根據環路的特性選取,它們值的選取是整個環路跟蹤性能的關鍵。 C_{1}主要決定了環路捕捉帶的大小,C_{2}則決定了環路的長期跟蹤速度和環路捕獲速度。C_{2}較大時,環路將經過相當長的時間才能成功入鎖。若用一個固定的環路濾波器,由于鎖定時間和精度的不同要求,捕捉時間遠小于跟蹤時間,這樣得到的結果顯然不是最優的。為了使環路既具有快速捕獲的能力,又能在跟蹤狀態時僅在平衡點附近有細微擺動,使輸出相位平緩變化,故應使環路和步進具有自適應調整的能力。可以采用環路切換法,即在不同時刻轉換環路濾波器的參數。

環路的Matlab仿真

分別利用正弦鑒相器和反正切鑒相器,在Matlab中仿真一個連續波的跟蹤過程。生成連續正弦波的頻率為10MHz,采樣頻率為80MHz,初始相位為30 。利用圖1的環路電路,通過設置環路濾波器的參數,仿真其跟蹤過程,并對跟蹤結果分析。

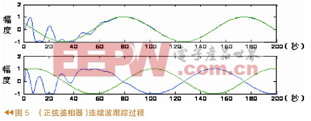

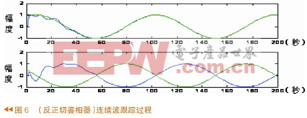

跟蹤過程如圖5所示。橫坐標為時間,縱坐標為信號幅度。圖5、6分別是利用正弦鑒相和反正切鑒相后,NCO的同相和正交輸出,同相輸出即為跟蹤結果。對比可知,反正切鑒相時40s就可以實現正確跟蹤,而正弦鑒相則要到80s才能實現。

比較正弦和反正切鑒相器的輸出(圖略),開始時輸出誤差較大,通過環路的調整,輸出誤差信號逐漸減小,最終趨于穩定。穩定后的輸出最小值是鑒相器的最小分辨率,即為跟蹤精度。跟蹤精度除了和鑒相器本身特性有關,還和環路濾波器的參數設置有關。通過對比可知,利用正切鑒相器比正弦鑒相器實現跟蹤速度快。

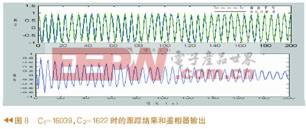

另外對環路濾波器取兩組不同參數時環路的性能分別進行了仿真。數字環路濾波器在環路中對輸入噪聲起抑制作用,并且對環路的校正速度起調節作用。采用理想二階環,設置C_{1}和C_{2},采用反正切鑒相器,仿真結果如圖7、圖8。圖7是 C_{1}=1200、C_{2}=16時的環路的跟蹤結果和鑒相器輸出,圖8是C_{1}=16039、 C_{2}=1622時環路的跟蹤結果和鑒相器輸出。橫坐標為時間,縱坐標為信號幅度。從圖7中可以看出,環路在10s左右即可以實現跟蹤,相應的鑒相器的輸出也很快維持在0值的附近。如圖8,當C_{2}較大時,跟蹤時間明顯延長,鑒相器的輸出波動很大。

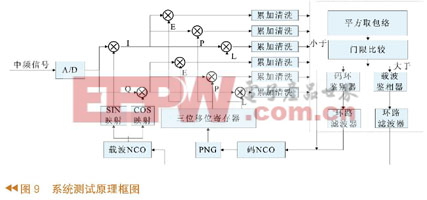

環路測試

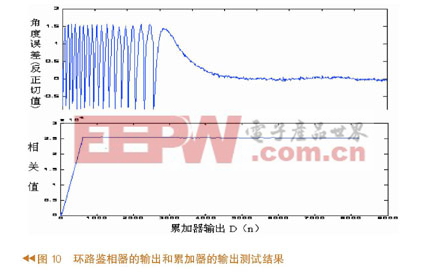

在系統測試中,測試原理如圖9所示,在-5dB條件下,載波環帶寬為40Hz,碼環帶寬為10Hz。對載波環路進行測試,載波環鑒相器及累加器的輸出如圖10所示。在穩定跟蹤后,累加器的輸出穩定在一個相對固定的數量級上。

結束語

科斯塔斯環由于對載波上的調制信息不敏感,在直擴導航數字接收機中被普遍采用。本環路設計已在一款測距接收機中得到應用,在一片FPGA(EP1C12Q240C8)上編程實現。經測試,在系統可提供33dB的擴頻增益的條件下,輸入信噪比高于-30dB時,環路正常工作,在-5dB時,多普勒頻移±2kHz條件下,經本載波跟蹤環路后殘余頻差小于1Hz,殘余相差小于3°。

鑒相器相關文章:鑒相器原理

評論