基于FPGA及DSP Builder的VGA接口設計

Avalon MM接口控制

在DSP Builder中,Altera提供了本設計與SOPC的接口――Avalon MM接口。

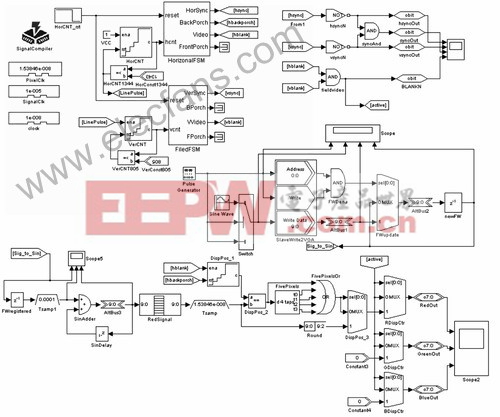

Avalon MM接口定義的接口信號主要有片選、讀使能、寫使能、地址,以及數據等。根據外設的邏輯,選用不同的接口定義信號,通過這些信號Avalon主端(CPU)可以向掛在Avalon總線上的從端外設寫地址與數據信號,Avalon主端外設也可以主動去獲取Avalon總線上的SRAM或SDRAM中的數據。不管是主傳輸還是從傳輸,都需要符合Avalon總線的讀寫時序才能發起一次正確的數據傳輸。可以利用Avalon MM接口將DSP Builder中設計的模塊做成自定義外設。NiosⅡ CPU就可以利用Avalon總線與DSP Builder中產生的自定義外設進行通信,在本設計中對集成到SOPC系統上的VGA接口的地址賦值為0x1后,數據寫入0x1,VGA接口控制器接收到數據,就會根據設計產生VGA時序信息及RGB信號,在屏幕上顯示圖像。圖3為整個一維信號VGA顯示系統的結構圖。

圖3 系統結構圖

仿真與硬件驗證

本設計在2C70 DSP硬件開發平臺下驗證。

借助于DSP Builder中的Signal Complier模塊,可以容易地將設計完成的系統直接轉化成RTL級的硬件描述語言,在QuartusⅡ下完成VGA時序的驗證與正弦波信號的下載與顯示。

從顯示器上硬件仿真結果來看,正弦波的幅度在有效的顯示區域內呈周期性變化,因此當顯示器與VGA口的J21相連時,屏幕上正弦波幅度在設計的范圍內顯示,一幅屏幕所顯示的周期數和DSP Builder中所設定的一致。在此基礎上還可以調整正弦波的采樣頻率,控制正弦波的顯示頻率與幅度大小,實現示波器的功能,觀察FPGA內部的信號。

結語

隨著VGA接口的廣泛使用,這種結合FPGA與DSP Builder的系統級設計方法已經展現優勢。從整個設計流程來看,系統的靈活性強,可靠性高,設計周期大大縮減,成本降低,且系統的可擴展性強。未來,VGA接口的圖像與視頻監控系統應用將會很有市場。

評論