基于FPGA及DSP Builder的VGA接口設計

VGA接口標準

VGA顯像原理

顯示器通過光柵掃描的方式,電子束在顯示屏幕上有規律地從左到右、從上到下掃描。在掃描過程中,受行同步信號控制,逐點往右掃,完成一行掃描的時間倒數為行頻;同時又在行同步脈沖期內回到屏幕的左端,從上往下形成一幀,在垂直方向上受場同步信號控制,完成一幀的時間倒數為場頻。圖像的顯示過程即為在電子束掃描過程中,將地址與圖像的像素依次對應,每一個被尋址的像素只獲得其自身的控制信息,而與周圍的像素不發生干擾,從而可以顯示穩定的圖像。

VGA接口是顯示卡上輸出模擬信號的接口,也叫D-Sub接口。這種接口上面共有15個針孔,分成3排,每排5個,通過模擬VGA接口顯示圖像的工作原理,將計算機內部以數字方式生成的顯示圖像信息,通過顯卡中的ADC轉變為R、G、B三基色信號和行、場同步信號,通過電纜傳輸到顯示設備中。

VGA時序

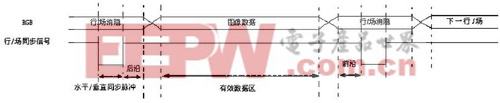

VGA的時序包括水平時序和垂直時序,且兩者都包含的時序參數有:水平(垂直)同步脈沖、水平(垂直)同步脈沖結束到有效顯示數據區開始之間的寬度(后沿)、有效顯示區寬度、有效數據顯示區結束到水平(垂直)同步脈沖寬度開始之間的寬度(前沿)。水平有效顯示區寬度與垂直有效顯示區寬度邏輯與的區域為可視區域,其他區域為消隱區。

一行或一場的時序信息如圖1所示。

圖1 行/場時序圖

根據目前的顯示器性能參數,以LG 505E為例,其最大分辨率已可達到1024×768@60Hz,水平掃描頻率30kHz54kHz ,垂直掃描頻率50Hz120Hz,帶寬75MHz。

基于DSP Builder的VGA接口設計方法

本設計需要完成的功能包括產生VGA時序以及基于VGA接口的信號顯示。設計符合VGA接口標準的接口系統,在該系統下可顯示一維矢量信號與二維圖像信號,并體現系統的可集成性,將該接口集成到SOPC系統中。

系統時鐘確定

根據系統時鐘計算公式:

時鐘頻率=(行像素數+行消隱點數)×(一場行數+消隱行數)×刷新率。

對于標準的VGA接口時序640×480@60Hz而言,時鐘頻率為800×525×60=25.175MHz。

在本設計中我們采用1024×768@60Hz的XGA顯示方式,因此系統的時鐘頻率PixelClk=1344×806×60=64.99MHz。

狀態機設計

由VGA時序可設計有限狀態機來完成時序信號,以本設計1024×768@60Hz為例,對于行同步信號設計四個狀態,即行同步脈沖信號區(horsync)、后沿區(backporch)、數據區(video)以及前沿區(frontporch)。用計數器hcnt的值來區分各階段信號,最大記數值為1344。場同步信號也設計成如上四個狀態,當完成一行的掃描后場計數器vcnt開始計數,因此一場可以有多行。

VGA DAC芯片及相應信號的生成

一般的VGA DAC芯片需要輸入相應的驅動信號才能工作,包括時鐘信號、同步信號、有效顯示區信號等。系統所用DAC芯片為FMS3818,其信號包括時鐘與數據信號(RGB)輸入、控制信號輸入(sync與blankn)以及RGB信號DA輸出。行同步與場同步信號與經VGA DAC產生的RGB數據信號一并輸出到VGA接口,驅動CRT顯示。在本設計中時鐘信號65MHz、同步信號為horsync與versync相與產生,有效顯示區信號為行與場的有效數據區信號相與產生。

一維矢量信號顯示方式

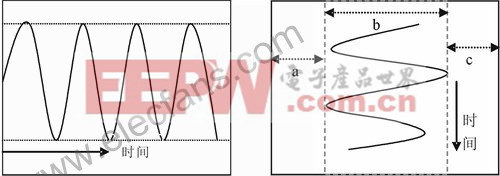

在二維的空間中顯示一維矢量信號,常規顯示方法可以是將一維信號從左至右顯示,如圖2(a)所示,就如在普通的示波器上觀察到的一樣。這樣,在VGA顯示時,一行掃過多個采樣點,需把要顯示的采樣點位置計算出來,當行信號掃過時,把采樣點的值賦給像素點,就完成了信號的顯示。而對于連續的一維信號,因為行頻比場頻高,圖2(b)的顯示方法更加合理。為此,將一維信號的時間軸映射到垂直方向上,幅值映射到水平方向上,當行掃描信號掃過一行時,映射一維信號的一個采樣點,即一行信號對應一個像素,當完成一行信號后接著回掃,開始掃下一行。一般情況下,場頻確定后,就可以根據一維信號的頻率確定出一場可以顯示的周期數,當完成一場信號后,在屏幕上就顯示一幀圖像。

在具體實現時,需要對一維正弦波信號的參數作兩點控制:控制正弦波的頻率,保證一行掃描對應一個采樣點;控制正弦波的幅度,將其控制在1024×768的有效顯示區域中。

對正弦波頻率來說,如果頻率太高,一行會掃到多個采樣點;如果頻率太低,一整屏無法顯示一個完整周期的信號。在本設計中,用一個較低的采樣時鐘控制正弦波的采樣,正弦波存放在一個查找表中。如果要在一屏中顯示n個周期的正弦信號,那么需要的采樣頻率fs=刷新率×n×查找表中一個周期的點數。

控制正弦波幅度即讓正弦波的最大值不能超出屏幕的顯示區。VGA有效顯示寬度為1024,則屏幕兩端的空閑部分寬度(圖2(a)和(c))都為100。

(a) (b)

圖2 一維正弦波VGA顯示示意圖

二維圖像信號的顯示方式

二維圖像的顯示過程較一維信號容易實現。對二維圖像,可以將二維圖像信號轉變成一維像素序列。在屏幕顯示區域內,當行與場同步信號掃過時,將該像素點對應的RGB值進行賦值,就可以完成二維圖像的顯示。對于本設計,VGA時序為1024×768模式,圖像的像素數在這個范圍內可以完全在屏幕上顯示,不會發生像素丟失。如果圖像比較小,還可以將圖像控制在屏幕的任意區域內。由于圖像大小受存儲空間限制,如果想要實現更高像素點的圖像,就必須借用外部的SRAM或SDRAM來做圖像緩存。

評論