基于中檔FPGA多相濾波器的設計實現

針對這些例子的用途,我們假設內插因子為L = 4,主時鐘頻率為FHz。正如先前所討論的,向上采樣(插入零值樣本的過程)發生在濾波操作之前。

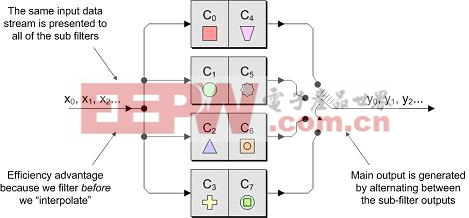

現在讓我們來考慮一個最初的多相實現,我們原來的8抽頭FIR濾波器被分成四個2 抽頭子濾波器,如圖16所示。

在這種情況下,相同的輸入數據流面向所有的四個子濾波器,在子濾波器輸出之間輪流產生主輸出數據流。最終的結果是,多相實現含有如同我們的常規8抽頭FIR濾波器相同數量的乘法器和加法器。然而,因為在內插之前進行了濾波,子濾波器只需要以1 / 4的主時鐘頻率運行,從而大大節省了功耗(這里主時鐘用于子濾波器輸出之間的采樣)。

此外,多相實現不需要向上采樣(零值插入)的邏輯。當然,我們可以用完全運行于主時鐘頻率和復用系數的單個2抽頭子濾波器取代原來的多相濾波器實現。

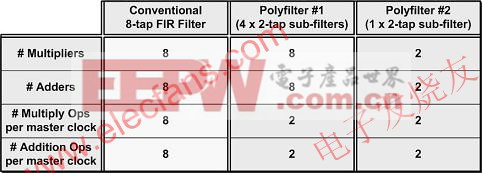

內插實現的這些例子的總結見表2 。

表2內插實現實例的總結

總結

DSP設計人員的工具箱的支柱之一是有限脈沖響應( FIR )濾波器。FIR濾波器越長(有大量的抽頭),濾波器的響應越好。但是更多的抽頭增加了邏輯要求、增加了計算的復雜性,增加了功耗,以及有更大可能的飽和/溢出。

多相技術3可用于實現濾波器,提供可比較的結果,而使用較少的邏輯,需要更少的計算資源、消耗更低的功率,并減少了可能的飽和/溢出。

所有這一切都意味著,多相基于濾波器的抽取器、內插器和重采樣功能是非常適合用更小的中檔FPGA來實現,如Lattice半導體公司的擁有SERDES功能的LatticeECP3系列,它具有高性能的sysDSP模塊。它的特點是有dual-slice結構,具有級聯/鏈接DSP slice和模塊的功能,增強的DSP指令集使LatticeECP3系列能夠引人注目地用于范圍廣泛的數字信號處理的應用,包括那些需要傳統的FIR和基于多相的濾波功能。

評論