利用布線技巧提高嵌入式系統(tǒng)PCB的信號完整性

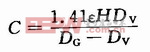

過孔的寄生電容給電路造成的影響主要是使數(shù)字信號上升沿減慢或變差,降低了電路的速度。過孔的寄生電容值越小,影響越小。若過孔在鋪底層上的隔離孔直徑為DG,過孔焊盤的直徑為Dv,PCB厚度為H,板基材料介電常數(shù)為ε,則過孔寄生電容C的大小近似于:

過孔寄生電感的主要影響是降低了電源旁路電容的有效性,使整個電源供電濾波效果變差。若L為過孔的寄生電感,h是過孔的長度,DH是中心鉆孔的直徑,則可以用下面的公式來簡單計算一個過孔近似的寄生電感:

![]()

從上式可以看出,過孔直徑對電感的影響較小,過孔長度對電感影響較大。在PCB中,通常旁路電容一端通過一個通孔連接到地平面,另一端也通過一個通孔連接到電源平面,因此通孔電感的影響會增加1倍。

2.3 傳輸線拐角對傳輸通道信號完整性問題的貢獻

當信號沿均勻連線傳播時,不會產(chǎn)生反射和傳輸信號的失真。但傳輸線上的拐角會使傳輸線處的阻抗發(fā)生變化,致使信號出現(xiàn)部分反射和失真。根據(jù)導(dǎo)線單位長度電容C1(單位:pF/in),導(dǎo)線線寬ω(單位:in),可通過下面公式簡單估算每個拐角的寄生電容Ccorner:

![]()

在高密度電路板中信號線線寬較窄時,其拐角的寄生電容量引起的時延累加一般不太可能對信號完整性有很大影響。但對于高頻敏感電路,如高頻時鐘線路,應(yīng)考慮拐角寄生電容所產(chǎn)生的累加效應(yīng)。

3 利用布線技巧抑制信號完整性問題

當信號從驅(qū)動源輸出時,構(gòu)成信號的電流和電壓將互連線看作一個阻抗網(wǎng)絡(luò)。當信號沿阻抗網(wǎng)絡(luò)傳播時,它不斷感受到互連線所引起的瞬態(tài)阻抗變化。如果信號感受到的阻抗保持不變,則信號不失真。一旦阻抗發(fā)生變化,信號就會在變化處產(chǎn)生反射,并在通過互連線的剩余部分時發(fā)生失真。如果阻抗改變程度足夠大,失真就會導(dǎo)致錯誤的觸發(fā)。在信號完整性優(yōu)化設(shè)計過程中,一個重要的設(shè)計目標就是:將所有的互連線都設(shè)計成均勻傳輸線,并減少所有非均勻傳輸線的長度,讓整個網(wǎng)絡(luò)中的信號所感受到的阻抗保持不變。基于此,可以歸結(jié)出一些利用布線技巧抑制信號完整性問題的方法:印制導(dǎo)線的走線形狀不要纏結(jié)、分支或硬拐角,盡量避免T形線和樁線;盡量保持同一網(wǎng)絡(luò)信號線的線寬,減少線寬變化;減少傳輸線長度,增大導(dǎo)線寬度;要盡量增大導(dǎo)線間的距離;盡量減少高速信號線的過孔及拐角,減少信號線的層間轉(zhuǎn)換;合理選擇過孔的尺寸大小;減小信號環(huán)路面積及環(huán)路電流。總之,任何改變橫截面或網(wǎng)絡(luò)幾何形狀的特征都會改變信號所感受到的阻抗。布線中減少信號完整性問題的重點就是減少傳輸線上的阻抗突變,讓整個網(wǎng)絡(luò)中的信號所感受到的阻抗保持不變。

4 結(jié)語

隨著嵌入式系統(tǒng)的發(fā)展,信號完整性成為嵌入式系統(tǒng)PCB設(shè)計中的一項極其重要的內(nèi)容,影響著整個PCB設(shè)計的成敗。在電路確定、元器件選定、PCB布局確定的情況下,可通過布線技巧來抑制信號完整性問題的出現(xiàn),提高PCB的可靠性,將信號完整性問題引發(fā)的損失降到最低。

評論