基于Virtex-5 FPGA的音視頻監(jiān)視系統(tǒng)設(shè)計(jì)

時(shí)序考慮事項(xiàng)和約束定義

生成并實(shí)現(xiàn)IP之后,下一步是執(zhí)行時(shí)序。我們對(duì)所有輸入時(shí)鐘的周期、抖動(dòng)和輸入偏移延遲進(jìn)行了約束,并且設(shè)置了相對(duì)于源時(shí)鐘的所有輸出延遲和輸入對(duì)輸出的延遲。然后在用戶約束文件(UCF)中建立了時(shí)序和布局約束。

我們將所有輸入時(shí)鐘約束為特定頻率,并且用以下UCF代碼定義了抖動(dòng)輸入:

NETi_clk_200_sTNM_NET=IN_200_CLKGRP;TIMESPECIN_200_CLKGRP=PERIOD5nsHIGH50%INPUT_JITTER0.1ns

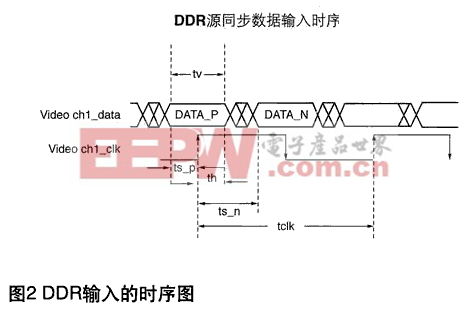

對(duì)于源同步數(shù)據(jù),在SDR的情況下,我們可以將輸入時(shí)鐘設(shè)置為0度相移或180度相移,而在DDR的情況下可以將其設(shè)置為90度相移。圖2所示為時(shí)鐘在90度相移時(shí)的源同步DDR數(shù)據(jù)輸入時(shí)序。

圖2所示為時(shí)鐘在90度相移時(shí)的源同步DDR數(shù)據(jù)輸入時(shí)序

對(duì)于PCIExpress核和千兆位以太網(wǎng)MAC核上的時(shí)序約束,我們按照CORE Generator示例中的定義對(duì)Block RAM和PLL/DCM使用了所有時(shí)序和布局約束。

因?yàn)樵S多Virtex-5設(shè)計(jì)都使用多個(gè)異步時(shí)鐘,所以我們必須在設(shè)計(jì)中定義偽通路,以使這些時(shí)鐘不受影響。

布局布線后的時(shí)序分析和時(shí)序校正

對(duì)設(shè)計(jì)進(jìn)行布局布線后,我們運(yùn)行了靜態(tài)時(shí)序分析(STA)和時(shí)序仿真,以了解是否存在其他時(shí)序錯(cuò)誤。對(duì)于STA,我們確保時(shí)序報(bào)告涵蓋了有約束和無(wú)約束的全部通路。通過(guò)使用STA報(bào)告,我們可以鑒定輸入/輸出時(shí)序和內(nèi)部系統(tǒng)時(shí)序。

事實(shí)證明,基于Virtex—5的FPGA非常適合我們的視頻監(jiān)視系統(tǒng)的要求。區(qū)域時(shí)鐘緩沖器和I/O時(shí)鐘緩沖器使我們能夠支持多信道源同步音視頻輸入。而且,該器件的PCI Express和千兆位以太網(wǎng)MAc硬宏為我們提供了進(jìn)行遠(yuǎn)程監(jiān)視所需的全球連接能力。

在未來(lái)的設(shè)計(jì)工作中,我們將可依靠前期規(guī)劃來(lái)確保有效使用特定FPGA的可用資源,設(shè)計(jì)出具有附加價(jià)值的產(chǎn)品。

評(píng)論