基于Virtex-5 FPGA的音視頻監視系統設計

引言

本文引用地址:http://www.104case.com/article/151332.htm本文探討在Virtex-5 FPGA中實現設計的一些難題,然后用一個項目作為示范來詳解充分利用其功能集的技法。設計過程包括幾個步驟,從針對應用選擇適合的Virtex-5開始。為便于本文敘述,我們假定IP模塊已經過匯編,并且已經就緒備用或已經用CORE Generator生成。

針對應用選擇適合的器件

多數音視頻采集器件都支持單信道,以Y/Cr/Cb數據格式生成源同步數字信號。DSP雖然有能力采集數字音視頻信號,也能夠執行數字信號處理任務,但通常卻僅支持少數幾條信道。本設計選擇了FPGA,事實證明這對于多信道輸入任務和信號處理任務都是良好的替代方案。

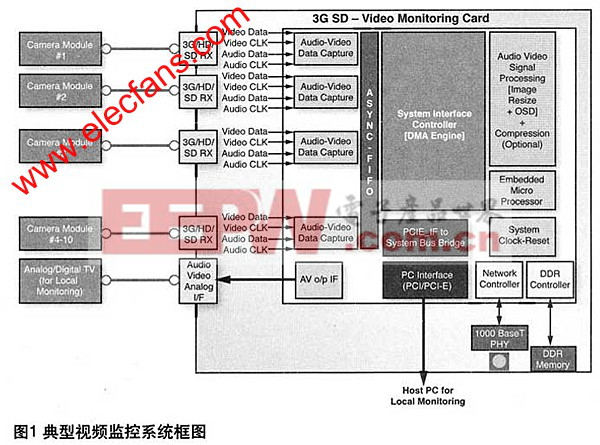

圖1所示為典型的安全視頻監視系統,其中有一個3G/SD/HD/SDI視頻接口。在此設計中,攝像頭將3G—SDI格式的信息傳送到電路板,后者繼而收集數據,并且以145.5MHz的最高時鐘頻率將其轉換成10位(Y/Cr/Cb格式)的源同步視頻數據(10/20位的接口)。電路板以 96kHz的最高時鐘頻率處理源同步音頻數據。

這里,存儲器的容量是512Mb,寬度是32位,所以FPGA必須支持高達2Gb的擴展能力。

對于這個設計來說,FPGA必須支持多達十條數字音視頻源同步輸入信道(20位源同步Y/Cr/Cb數據格式),并且必須可按照SD/HD數據格式配置。其他要求還包括音視頻信號處理和可選壓縮算法、帶有高級DMA引擎的中央處理單元和一個用來連接VGA顯示器或標準型電視機的音視頻輸出端口等。

要滿足這些技術條件,在實現設計時必須考慮幾個因素。其中的主要因素是時鐘要求分析、初始布局規劃、核生成和IP集成、時序約束定義以及布局布線后的時序分析和時序校正。但首先要決定FPGA的選擇。

FPGA的選擇

我們根據幾個因素進行選擇。器件需要滿足預計的I/O要求,并且必須具有相應數量的邏輯單元、適宜的Block RAM尺寸以及一定數量的時鐘緩沖器和時鐘管理器件,如鎖相環(PLL)、數字時鐘管理(DcM)模塊和乘累加模塊。基于這些需求,我們選擇了 Virtex-5 XCVSX95T-FF1136。

時鐘要求分析

選擇FPGA之后,我們開始設計過程,即分析時鐘控制要求,然后將信號映射到I/O組或I/O引腳。

對于時鐘要求分析,重要的是考慮以下幾個因素:FPGA是否具有足夠的時鐘功能I/O線和全局時鐘I/O線?是否有足夠的PLL、DCM和全局時鐘緩沖器?全局時鐘I/O緩沖器是否支持所要求的最高頻率?

本設計的時鐘控制要求包括:一個以150MHz-200MHz頻率運行的全局系統時鐘,具有若干PLL供所有內部邏輯用來進行處理;一個以 250MHz頻率運行的全局時鐘,具有PLL/DCM的PCI Express鏈接;一個以250MHz頻率運行的全局時鐘緩沖器(帶有PLL和DCM)用于以太網MAC;以及一個200MHz的時鐘(由 PLL/DCM生成),用于I/O模塊中的逐位去歪斜等。

我們總共需要4~6個全局時鐘緩沖器和16個局部時鐘緩沖器。FPGA XCVSX95T-FF1136提供每組20個全局時鐘輸入引腳和4個時鐘功能I/O。也可將I/O組的時鐘功能引腳直接連接到區域緩沖器或I/O緩沖器,并且將其用于特定區域或相鄰區域。另外,各GTP/MGT還有一個參考時鐘輸入引腳。

初始布局規劃

初始布局計劃是設計的關鍵階段,因為此時所作的決定將確定最終設計是否能滿足時序。其中組選擇和引腳分配是布局規劃的重要步驟。如何進行這兩個步驟取決于FPGA周圍其他組件的布局。

Virtex—5 FPGA共有18個I/O組,可以將各種輸入/輸出對映射到這些I/O組。有幾個I/O組支持20對輸入/輸出或10個全局時鐘。其他I/O組則大多支持 40對輸入/輸出,每對輸入/輸出上有4個輸入時鐘功能引腳和8個輸出時鐘功能引腳。

同時,上下兩牛個FPGA包括三個時鐘控制模塊(CMT),即一個PLL和兩個DCM。對于需要上下兩半個器件中的PLL的所有全局時鐘信號,我們必須確保予以妥善映射,以使設計具有從全局時鐘輸入緩沖器到PLL的直接連接。然后我們使用剩下的14個I/O組,這些組支持40條I/O線,是單端/差分模式。每個組由4個單端時鐘功能引腳和8個差分時鐘功能引腳組成。接下來可以將時鐘功能引腳映射或連接到區域時鐘緩沖器或I/O時鐘緩沖器。

評論