基于ARM微處理器的機載語音告警系統設計

摘要:針對某型現代軍用飛機的研制要求,設計了基于ARM微處理器的機栽語音告警系統。該系統硬件設計采用立體數字語音轉換器,并對語音采 用差分方式輸出以提高抗干擾能力,設計了50 ms掉電保護。軟件采用U-Boot的移植及告警命令優先級的調度處理技術,并將大語音庫從NAND Flash直接加載到SDRAM中,減小發音間隔。其應用結果表明,該機載語音告警系統能根據戰場形勢變化解析告警命令后對飛行員發出告警語音,并且接收 到告警命令到發出告警語音間隔小于40 ms,適應現代復雜多變的戰場環境,告警語音音質清晰、無間斷音。

關鍵詞:語音告警;ARM;音頻芯片;掉電保護;U-Boot的移植

飛機語音告警系統是新型飛機必備的一種機載設備,其作用是將飛機當前的工作狀態、危險狀況或者通過數據鏈獲取的作戰任務命令,實時以語音方式告知飛行員。 在飛機飛行過程中飛行員一般是通過安裝在座艙里的操作臺、儀表和告警信號燈來了解飛機各個系統的工作狀態。由于飛行員在飛行時為完成相應的飛行任務,注意 力高度集中在飛行高度、速度和雷達參數等數據信息上,對飛機故障信息的注意力要相對弱一些,這樣就會出現飛行員不能及時地對故障采取措施,從而導致嚴重的 飛行事故。同時,目前大多數新研制或改裝的飛機都有數據鏈系統,許多作戰任務命令不再單純依靠地面指揮人員或長機的語音傳達,可通過數據鏈或根據戰場態勢 產生,并及時告知飛行員,因此,針對某新型飛機的研制要求,設計了基于ARM單片機的語音告警系統。

1 系統總體框架設計與工作原理

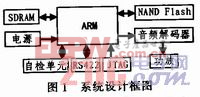

語音告警系統由以下6部分組成:語音命令輸入單元、語音命令真偽和優先權判斷單元、告警語音播放單元、電源及其監控單元、自檢測單元和調試接口,系統設計框圖如圖l所示。

系統的語音告警數據可以通過JTAG預先裝載到非遺失的NAND Flash中,系統上電后自動將告警軟件和語音告警數據加載到SDRAM中。系統工作時,通過RS422接收外系統傳來的一個或多個告警命令,按照告警命 令的優先級依次發出告警語音。當新的告警命令優先級高于當前告警命令時,中斷當前告警語音;當高優先級的告警命令處理結束后,接著依次發出較低一級的告警 語音。

2 硬件設計

2.1 ARM處理器單元

ARM處理器單元由S3C2440型ARM、存儲單元的NAND Flash和SDRAM組成。

2.1.1 S3C2440尋址原理

S3C2440是基于ARM920T內核的16/32位RISC微處理器,提供32位地址總線,可以訪問4 Gb的線性地址空間,而S3C2440的內部地址總線是30 b,能夠訪問的最大外部地址空間是1 GB,可見S3C2440僅利用ARM920T32位地址空間的低30位。S3C2440將1 GB的外部地址空間分成了8個存儲器組,每個組的大小128 MB,其中6個用于ROM、SRAM等存儲器,2個用于ROM、SRAM、SDRAM存儲器。S3C2440對外尋址時,采用了部分譯碼的方式,低位地址 線用于外圍存儲器的片內尋址,高位地址線用于外圍存儲器的片外尋址。高3位ADDR[29:27]來選擇該地址屬于哪一個

存儲器組,ADDR[26:0]來實現相應存儲器組的內部尋址,尋址范圍為128 MB,從而使得其外圍地址訪問空間為1 GB。

2.1.2 存儲單元設計

NAND Flash接口信號較少(如圖2所示),數據寬度只有8 b,沒有地址總線,地址、數據總線復用,串行讀取,以頁(page)為單位進行讀寫,以塊(block)為單位進行擦除。操作NAND Flash時,先傳輸命令,然后再傳輸地址,最后讀寫數據。本系統采用64 Mx8 bit的K9F1208,其組織方式可以分4類地址:

1)Column Address表示數據在半頁中的地址,大小范圍0~255,用A[0:7]表示;

2)Hafpage Pointer表示半頁在整頁中的位置,即在O~255空間或256~511空間,用A[8]表示;A[8]=00為上半頁,A[8]=01為下半頁;

3)Page Address表示頁在塊中的地址,大小范圍0~31,用A[9:13]表示;

4)Block Address表示塊在flash中的位置,大小范圍0~4 095,A[14:25]表示。

對NAND Flash操作時,地址分4個周期傳送。

評論