基于FPGA和硬件描述語言Verilog的液晶顯示控制器的設計

2 設計與實現

本設計的液晶顯示器刷新頻率為70Hz,每一幀周期為14.28ms,每一行周期為60μs,時鐘信號CP的頻率為2 MHz,將一行數據輸入列移位寄存器的時間為40μs,因此每一行設計了20μs的空白時間。

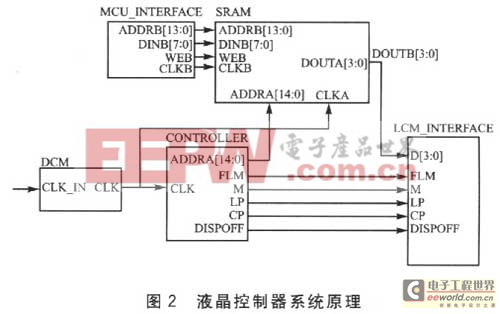

液晶控制器系統原理如圖2所示。時鐘模塊采用Xilinx公司的Coregen IP工具定制,數字時鐘管理器DCM模塊將FPGA 50 MHz時鐘信號CLK_IN 25分頻為2 MHz控制器時鐘信號CLK。DCM采用了數字延遲鎖相環技術來消除時鐘相位的位移,提供比自行分頻更穩定的時鐘信號,以滿足控制系統要求。CONTROLLER模塊為LCM提供滿足圖l所示時序要求的控制信號CP、LP、FLM、M、DISPOFF,并且同步產生SRAM的讀地址ADDRA[14:0]。

SRAM為內存模塊。為了提高輸入LCD的數據流速度.設計了32K×4位的艤端口內存,可同時實現讀/寫,并實現數據格式的轉化,由上位機MCU輸入的8位數據轉為輸入LCM列驅動器的4位數據;B端口由MCU_INTERFACE與上位機MCU連接,由MCU微控制器將顯示數據寫入內存SRAM。其中,ADDRB[13:0]控制16K×8位的寫地址,DINB[7:O]為寫入數據,WEB為寫有效控制,CLKB為寫時鐘;A端口由CONTROLLER模塊控制讀地址ADDRA[14:0],讀時鐘CLKA由系統時鐘信號CLK控制,DOUTA[3:0]將數據寫入LCM列驅動器。2.2 控制模塊設計

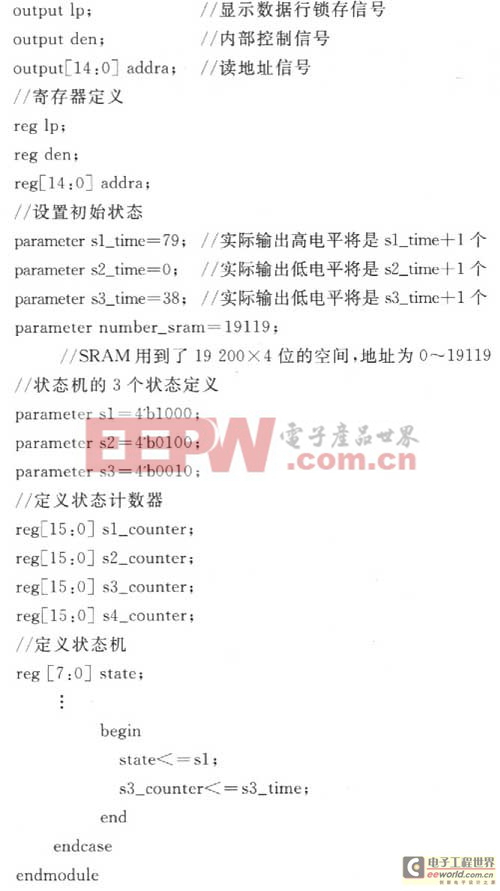

應用狀態機的方法,用Verilog硬件描述語言設計控制模塊CONTROLLER。CLK為2 MHz輸入時鐘信號。LP和內部控制信號DEN由狀態機1控制產生,FLM由狀態機2控制產生,M由狀態機3控制產生,CP信號和ADDRA[14:0]根據CLK和DEN信號控制得到。狀態機1有3個狀態:狀態1,LP為O,DEN為1,持續80個CLK脈沖后轉向狀態2;狀態2,LP為l,DEN為0,持續1個CLK脈沖后轉向狀態3;狀態3,LP為O,DEN為O,持續39個CLK脈沖后轉向狀態1。狀態機2有2個狀態:狀態1,FLM為l,持續1個LP周期時間,即120個CLK脈沖;狀態2,FLM為O,持續剩下的239個LP周期,即28 680個CLK脈沖。狀態機3有2個狀態,狀態l,M為1。持續1個FLM周期時間,即28800個CLK脈沖;狀態2,M為0,也持續1個FLM周期時間。CP信號和ADDRA由于含有空白信號,所以由內部控制信號DEN和時鐘信號CLK得到。以下為設計的源代碼初始化部分:

/Script> 3 仿真、下載測試分析

/Script> 3 仿真、下載測試分析

評論