基于MATLAB在FPGA 算法上浮點定點轉(zhuǎn)換的實現(xiàn)

浮點定點轉(zhuǎn)換是在 FPGA 上實現(xiàn)算法時最困難的地方(圖 1)。

本文引用地址:http://www.104case.com/article/151252.htm

雖然 MATLAB 是一種強大的運算開發(fā)工具,但其許多優(yōu)點卻在浮點定點轉(zhuǎn)換過程中被降低了。例如,由于定點算術中精度較低,新的數(shù)學誤差被引入算法。您必須重寫代碼,使用能夠反映實際硬件宏架構的低級模型來替換高級函數(shù)和運算符。而仿真運行時間將可能長達 50 倍之久。基于這些原因,MATLAB,這一算法開發(fā)的優(yōu)勢選擇,卻經(jīng)常遭到遺棄,轉(zhuǎn)而使用 C/C++ 進行定點建模。

生成定點模型

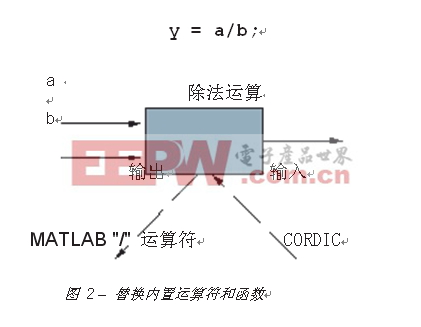

如果未將高級函數(shù)和運算符替換為硬件精確的宏架構,浮點 MATLAB 算法的定點表示將不會真正反映最終硬件的響應(圖 2)。

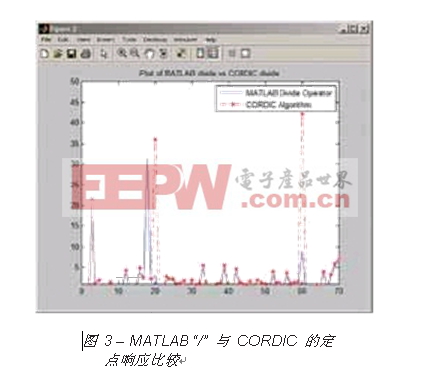

圖 3 對此進行了突出顯示,該圖使用一組量化為 8 位有符號二進制補碼的隨機輸入矢量,對 MATLAB 除法運算符與工具硬件 CORDIC 除法算法的定點響應進行了比較。

根據(jù)數(shù)據(jù)數(shù)值,計算輸出之間將存在巨大分歧。

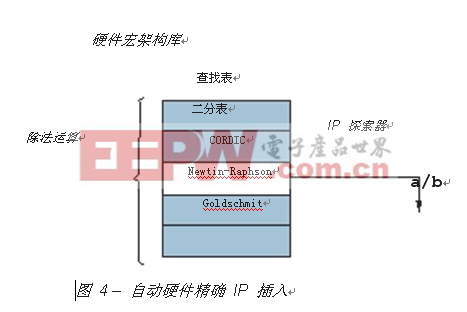

在定點生成過程中,AccelDSP™ Synthesis 綜合工具的 IP Explorer™ 技術將自動使用硬件精確的表達式替換高級 MATLAB 函數(shù)和運算符(圖 4)。此步驟是透明的,且不需要對 MATLAB 代碼進行修改。您可以使用綜合指示來重新定義初始宏架構和微架構選擇。

一旦這些運算符替換為硬件精確的宏架構,量化過程就將開始。

圖形輔助式自動量化

與定點 DSP 處理器不同, FPGA 結(jié)構允許使用可變定點字長。通過解除對變量的固定 16 位或 24 位邊界限制,您可以執(zhí)行需要位數(shù)增長的算術計算而不會引起額外的數(shù)值誤差。

這對于像雷達、導航和制導系統(tǒng)等要求較高數(shù)值精度的應用來說是一個巨大的優(yōu)點。

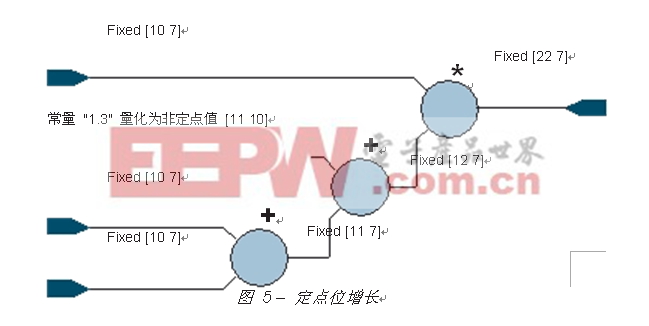

在大多數(shù)情況下,位增長率定律 (bit growth rules) 是簡單直接和易于理解的。例如,一次加法的結(jié)果增長一位,而一次乘法的結(jié)果則增長到等于輸入字長度的總長度(圖 5)。然而,要在實際設計中確定變量的這些屬性,將是一個高度反復的過程。允許未檢查的位數(shù)增長現(xiàn)象發(fā)生,在硬件中代價是昂貴的,通常也是不必要的。如果您技術功底深厚,您可以采用各種技巧來盡可能地減小字長而同時保持數(shù)值精度。

評論