具有低功耗意識的FPGA設(shè)計方法

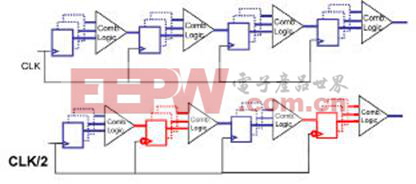

在降低時鐘樹的功耗方面,常用的方法有使用門控時鐘,對常用的流水線時鐘結(jié)構(gòu)進行修改,盡量使用FPGA內(nèi)部的全局時鐘資源等。通過對常用的流水線時鐘結(jié)構(gòu)在RTL級進行修改,就像在圖4中所看到的,做正反時鐘沿間隔,這樣時鐘頻率可以減慢一半,可以節(jié)省該時鐘路徑一半的功耗。同樣可以通過人工對時鐘域進行平面布局,來降低時鐘樹產(chǎn)生的功耗。這種方式對工程師的要求相對較高。Actel的設(shè)計師提供基于功耗驅(qū)動的布局布線策略。選擇該策略,布局布線工具自動會在滿足時序要求的情況下,盡可能的降低布局功耗。

圖4 對常用的流水線時鐘結(jié)構(gòu)在RTL級做修改

要降低邏輯和走線的功耗,需要調(diào)整綜合選項、了解算法/功能塊的架構(gòu)和功耗概況,通過減少信號的翻轉(zhuǎn)來降低功耗。不同的綜合選項和策略會對動態(tài)功耗有影響,基本上需要注意的是全局時序的設(shè)定以及set_max_fanout選項,以及是選用面積優(yōu)先還是時序優(yōu)先的綜合策略。

通過對DesignWare和一些私有的加法器和不同頻率下的功耗的評估,DesignWare下面的BK加法器在功耗方面是最友好的。針對同樣5%到10%的速度降級,BK加法器和其他的私有加法器的核相比,可以減少10%到15%的面積和功耗。在選擇乘法器的時候,必須要考慮乘法器的面積、功耗和速度。

計數(shù)器在設(shè)計中有不同的用法,有的用于計算事件發(fā)生的順序或者用掉的時間,有的用于驅(qū)動類似于RAM的地址總線、數(shù)據(jù)總線、狀態(tài)機的下一跳狀態(tài)或者輸出邏輯,有的用于當(dāng)輸出的值達到不同的解碼值時做不同的設(shè)定的處理。根據(jù)不同的用途可以考慮用二進制順序計數(shù)、格雷碼計數(shù)、環(huán)形計數(shù)的實現(xiàn)方法。如果計數(shù)器只是用于產(chǎn)生一些標(biāo)記,建議采用二進制的實現(xiàn)方式;如果計數(shù)器用于驅(qū)動一個大的負載總線,建議用格雷碼計數(shù)器;如果多個計數(shù)器的值需要被解碼,環(huán)形計數(shù)器是最佳選擇(譯碼邏輯是最小的)。

通過降低邏輯的翻轉(zhuǎn)率來降低動態(tài)功耗

首先在設(shè)計中,需要盡量避免不必要的翻轉(zhuǎn),可以通過下面幾個步驟來實現(xiàn)這一目標(biāo):首先分析哪些邏輯的翻轉(zhuǎn)是不必要的,隨后對不必要的邏輯翻轉(zhuǎn)的傳播進行限制,展開邏輯翻轉(zhuǎn)的時間。

減少邏輯可能產(chǎn)生的毛刺,先標(biāo)識出翻轉(zhuǎn)率高的網(wǎng)絡(luò)以及它們的驅(qū)動,然后對驅(qū)動單元輸入的最壞時序情況做評估,隨后將毛刺的源往前調(diào)或往后調(diào),然后對驅(qū)動單元的輸入的最壞時序情況做評估,最后在驅(qū)動的邏輯后面插入一級觸發(fā)器,根據(jù)先前的評估情況來決定用路徑上其他時序元件的相同時鐘沿或者相反的時鐘沿來驅(qū)動觸發(fā)器。即使是在單周期路徑上面,如果有足夠的slack來增加一個與門以及相關(guān)走線,那么就可以用與門的另外一個輸入(毛刺源驅(qū)動寄存器)的反相時鐘沿,從而減少毛刺。在某些情況下,可以通過伸展反轉(zhuǎn)時間來降低毛刺的峰值功耗。

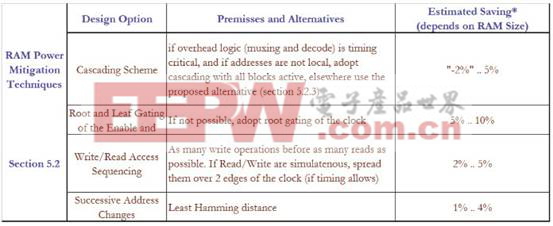

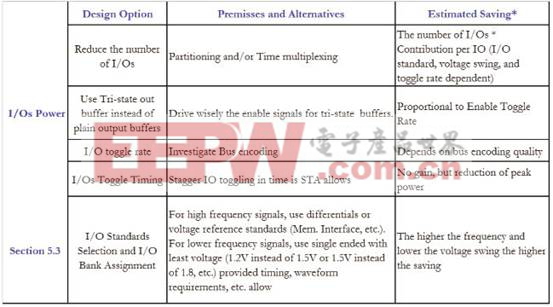

建議設(shè)計者要了解最終系統(tǒng)的運行模式,以及每種模式下系統(tǒng)的功耗概況。如果系統(tǒng)處于睡眠模式或者關(guān)閉模式的時間較長,需要觀察浪涌電流和編程電流的影響,并處理好靜態(tài)功耗。需要檢查設(shè)計的動態(tài)功耗概況,找出功耗的主要瓶頸,根據(jù)概括表(圖5~圖8)找出最好的解決方法。

圖5 RAM 動態(tài)功耗概括表

圖6 I/O功耗概括表

評論