Niosll和USB接口的高速數據采集卡設計

引 言

本文引用地址:http://www.104case.com/article/151090.htm隨著現代工業生產和科學研究對數據采集的要求日益提高,在瞬態信號測量、圖像信號處理等一些高速、高精度的測量中,都迫切需要進行高速數據采集(如雷達信號分析、超音波信號分析);而進行數字處理的先決條件是將所研究的對象數字化,因此數據采集與處理技術日益得到重視。在圖像信號處理、瞬態信號檢測、工業過程檢測和監控等領域,更是要求高速度、高精度、高實時性的數據采集與處理技術。現在的高速數據采集處理卡一般采用高性能數字信號處理器(DSP)和高速總線技術的框架結構。DSP用于完成計算量巨大的實時處理算法,高速總線技術則完成處理結果或者采樣數據的快速傳輸。DSP主要采用TI和ADI公司的產品,高速總線可以采用ISA、PCI、USB等總線技術。其中PCI卡或ISA卡安裝麻煩,價格昂貴,受計算機插槽數量、地址、中斷資源的限制,可擴展性差,在一些電磁干擾性強的測試現場,無法專門對其做電磁屏蔽,易導致采集的數據失真。通用串行總線USB是為解決傳統總線不足而推廣的一種新型的通信標準。該總線接口具有安裝方便、高帶寬、易于擴展等優點,已逐漸成為現代數據發展趨勢。基于USB的高速數據采集卡充分利用USB總線的上述優點,有效地克服了傳統高速數據采集卡的缺陷。

1 系統硬件設計

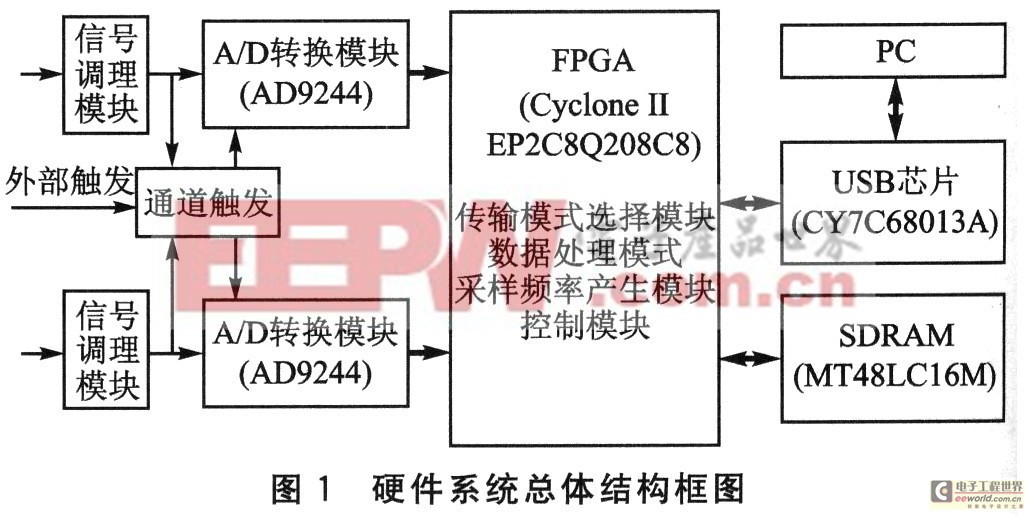

本系統主要是基于USB2.O的S1ave FIFO模式,在FPGA控制下完成雙通道、不同速率的數據的采集和發送,全兼容USB2.O總線接口標準,其數據的采樣率可高達65 Msps;適用于較高速動態信號的實時記錄采集,其硬件系統總體結構框圖如圖1所示。

該系統主要由信號調理模塊、A/D轉換模塊、觸發模塊、基于FPGA的主控模塊、USB收發控制模塊、片外存儲器及其他輔助電路組成。調理電路與A/D轉換器,將傳感器采集的模擬信號進行相關的信號調理后送入AD9244芯片轉換為數字信號。處理后的數據送往FPGA主控模塊,根據相關的控制信息,選擇通過直接傳輸給上位機,或者先存儲在外部SDRAM,然后經過相關的數字處理后再傳輸給上位機。

2 系統模塊介紹

2.1 USB2.0專用微處理器CY7C68013A

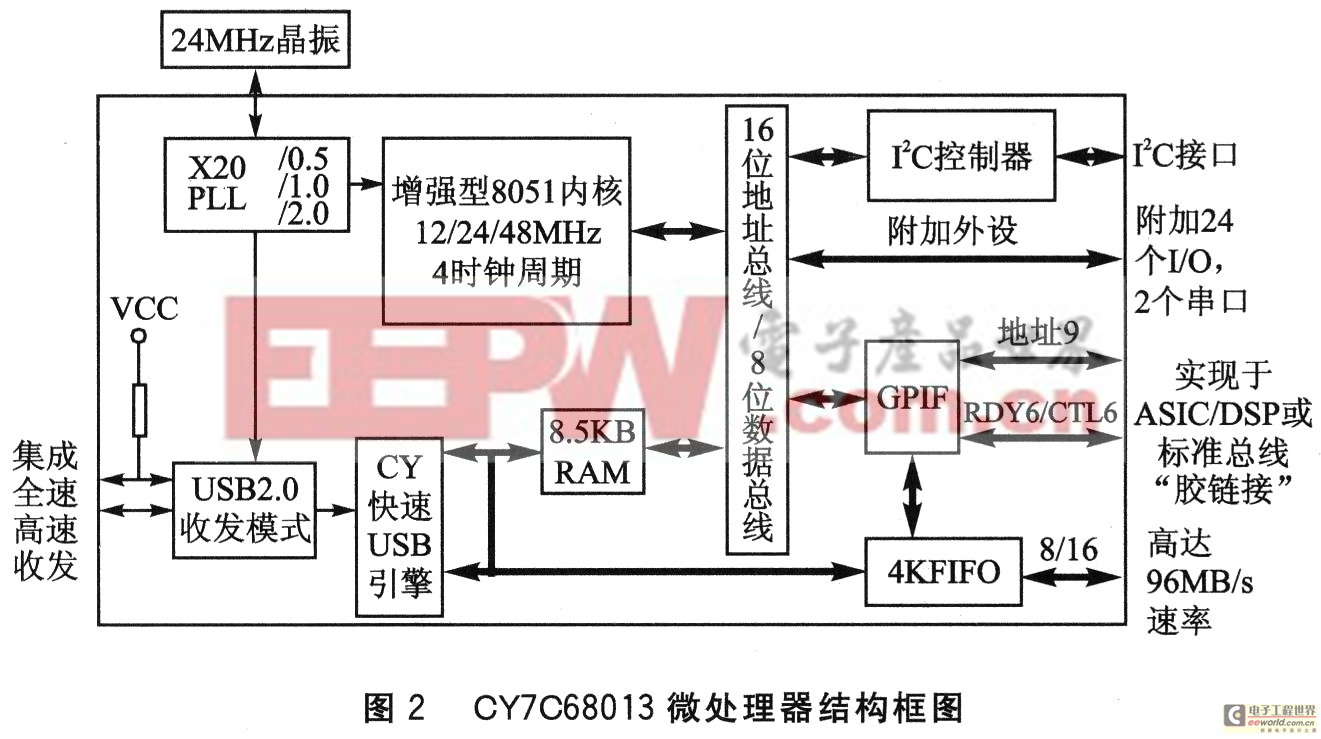

CY7C68013A是Cypress Semiconductor公司生產的一款集成USB2.O的微處理器。它有3種封裝形式——56SSOP、100TQFP和128TQFP,其結構框圖如圖2所示。

CY7C68013集成了USB2.O收發器、SIE、增強的8051微控制器和可編程的外圍接口部件。其SIE可在全速(12 Mb/s)和高速(480 Mb/s)兩種模式下運行,同樣可以使用內部RAM來進行程序和數據的存儲。GPIF和Master/Slave端口FIFO為ATA、UTOHA、EPP、PCM—CIA和DSP等提供了簡單和無需附加邏輯的連接接口。其編程可以根據設計的需要進行,不需要CPU的干預,只需通過CPU的一些標志和中斷即可進行通信。CY7C68013共有7個輸入輸出端口:EP0、EPlOUT、EPlIN、EP2、EP4、EP6、EP8,其中EP2、EP4、EP6、EP8可以分別被配置為批量/中斷/同步傳輸模式,傳輸方向均可配置為I/O,端口EP2、EP6的緩沖區大小可編程為512或1 024字節,深度可編程為2/3/4倍大小;端口EP4、EP8的緩沖區大小固定為512字節,深度為2倍,采用不同的配置方式,可實現特定帶寬和速率要求的數據傳輸。

評論