基于DSP+FPGA的紅外圖像小目標檢測系統設計

為節約程序運行時間,選取k的取值范圍為[μ+5σ…N],其中μ為整幅圖像的均值,σ為整幅圖像的平均差,直到找到使類間方差取最大值時的k值,即為最佳分割閾值th。

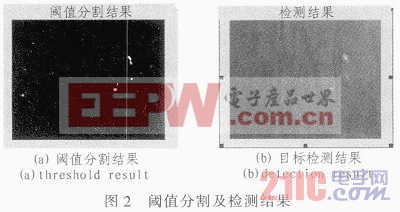

對經過Top-hat處理后的圖像,利用上述的最大類間方差法獲取閾值,利用這個閾值對圖像進行分割,最后通過判斷目標的形狀大小,以達到提取目標的效果,如圖2所示,圖2(a)為閾值分割的結果,圖2(b)為最終判斷結果。本文引用地址:http://www.104case.com/article/150965.htm

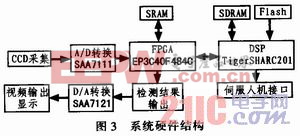

2 硬件系統結構

在實時視頻處理系統中,底層算法的數據量大,運算結構相對比較簡單,對速度有很高的要求,而高層處理算法控制結構復雜,數據量較底層算法少,故本文采用FPGA+DSP的結構。利用DSP實現目標檢測的算法,可以提高運行速度及便于調試和修改,FPGA實現整個系統的控制和圖像的基本預處理功能。整個系統的硬件結構如圖3所示。

在系統設計中,DSP采用ADI公司通用浮點型TigerSHARC201,它擁有非常高的存儲寬度,支持32位和擴展的40位浮點運算,支持8、16、32、64位定點運算。它擁有高達600 MHz的內核時鐘速率,一個周期可以執行4條指令,相當于24次16 bit定點操作或者6次浮點操作。處理器的運算流水是雙周期的,分支流水為2~6周期,鑒于此流水深度,它使用分支目標緩沖(BTB)來減少分支延遲,其兩個相同的計算單元均支持浮點和定點運算。每周期最多可執行4個32-bit寬的指令,因此很容易實現高性能的應用。

FPGA采用Altera公司的EP3C40F484C對視頻信號進行預處理和整個系統的時序控制,它具有多達24 624個邏輯單元,具有129個兼容的LV-DS通道,每個通道數據率高達640 Mb/s,還有4個可編程鎖相環和8個全局時鐘線。另外此芯片的功耗較低,全局運行時總功耗為300 mW左右。除此之外,FPGA作為系統的控制芯片還要為DSP及主機控制雙口SRAM接口、外部存儲器、視頻編碼器編碼等單元提供準確的邏輯時序和可靠的驅動電路。

2.1 視頻輸入和輸出模塊

采用解碼器SAA7111將攝像頭輸出的模擬視頻信號轉換為數字信號。SAA7111是飛利浦公司推出的9位視頻解碼器,提供6路模擬輸入和2個增強型的模數轉換器。通過配置SAA7111將PAL制式的模擬基帶信號轉化為CCIR-656格式的UYVY信號,并將其送入FPGA中,進行預處理。經過預處理后的圖像數據再由FPGA重新打包成CCIR-656格式的數據送入到TS201的Link口。具體連接如圖4所示,VPO[0…7]沒有數據輸入,VPO[8…15]是數據輸出管腳與FPGA相連,時鐘同步信號TS201采用MDMA的方式將原始圖像信號存入SDRAM中,供目標檢測算法使用。視頻輸出模塊采用視頻編碼器SAA7121,標準的UYVY數據從FPGA的引腳輸出,送到SAA7121的數據引腳,場、行同步信號分別接到FPGA的控制引腳上,通過行、場信號的控制,就能夠輸出顯示正確的視頻圖像。在SAA7111和SAA7121工作之前,都需要對這兩個芯片進行配置,它們的配置的參數都是通過FPGA產生I2C總線來實現的。

評論