一種基于DSP的音頻實時處理系統

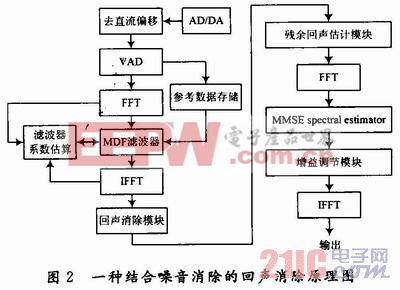

1.2.2 改進的回聲消除系統

如圖2所示,通過加入靜音檢測算法(VAD)對輸入信號的狀態進行判斷,不僅可以減輕實際的運算量,也可降低噪音對自適應濾波器的干擾,在一定程度上避免了濾波器發散的情況。同時加入MMSE Short-time Spectral Amplitude Estimator替代了傳統的非線性處理器(NLP)算法。在頻域內對參與回聲的頻譜能量進行估計,計算增益,最后達到相對平滑的殘余回聲和噪音的處理。本文引用地址:http://www.104case.com/article/150960.htm

通過對濾波器狀態參數的跟蹤,根據濾波器當前是否正常收斂,殘余回聲估計模塊的輸出結果會自動調節估計值的大小,避免在濾波器正常收斂的情況下,抑制殘余回聲導致處理后正常信號損失過多的問題。

圖2中采用的靜音檢測算法(VAD)采用了同時檢測短時能量與過零率的方法,保證了判斷的可靠性。在遠端語音不存在的時候,沒有必要進行回聲消除,只需要進行本地的噪音消除,若本地語音不存在則不需要做任何處理。

結合VAD系統更有效地減少了對噪音和回音估計的誤差范圍,通過對濾波器系數更新的學習和調整功能使得在雙方通話過程中音頻信號具備更好的信噪比。通過非線性信號檢測模塊加強了整體消除回音的能力。

2 基于DSP的音頻處理系統實現

2.1 硬件平臺

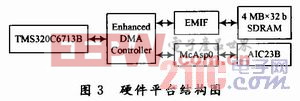

DSP的選型需要考慮運算速度、成本、硬件資源以及程序的可移植性等多個問題。由于算法的浮點特性,本文采用了美國德州儀器(TI)的TMS320C6713B浮點DSP作為核心處理器,通過使用JTEG標準測試接口、EDMA控制器、GIPO通用輸入輸出端口以及多通道音頻緩沖串口(McASP)等主要片外設備來完成系統的設計。

TMS320C6713B可以工作在225 MHz主頻上,片內有8個并行處理單元,分為相同的兩組,其體系結構采用甚長指令字(VLIW)結構,單指令字長為32 b,8個指令組成一個指令包,總字長為256 b。L1支持4 KB的程序緩存以及4 KB的數據緩存,L2支持64 KB的緩存。32 b的外部存儲器接口(EMIF)。與SDRAM等無縫連接,可以尋址256 MB。

由于系統運行過程中需要實現的算法較多,僅依靠TMS320C6713B的192 KB片內RAM來執行程序是很困難的。本文使用了EMIF的接口擴展了SDRAM作為算法和數據的存儲區域。采用TLV320AIC23B實現音頻輸入和輸出,AIC23支持48kHz帶寬、96kHz采樣率的雙聲道立體聲A/D,D/ A,音頻輸入包括了麥克風輸入和線路輸入。

系統的硬件平臺如圖3所示。

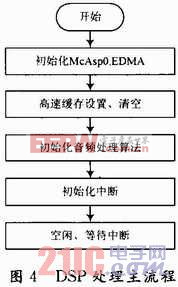

2.2 基于DSP的軟件實現

基于DSP的實時處理的實現,本文將AIC23采集到的數據先存儲到SDRAM中,在需要處理的時候利用EDMA實現Ping-Pong緩沖,將待處理的數據分批搬運到片內存儲器,結合高速緩存和片內內存設計合適的數據結構,并將數據對齊,這樣大大減小了數據搬移帶來的開銷。

DSP處理主流程圖如圖4所示。

評論