基于LZW算法的數據無損壓縮硬件實現

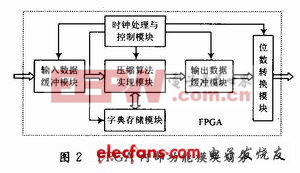

LZW數據壓縮算法的FPGA硬件實現,其內部功能模塊劃分如圖2所示。

2.2 各功能模塊說明

輸入/輸出數據緩存模塊完成FPGA所有數據傳輸工作,為了保證異步時鐘域數據同步,使用FPGA片內的Block RAM構成一個FIFO對輸入數據進行緩存。

字典存儲器模塊需要存放字典項的三部分內容:字典項編碼、前綴碼、當前碼。將存儲器的容量設計為1K。采用FPGA內部宏單元lpm-ram-dp(單口RAM)設計字典存儲器。

算法實現模塊要實現匹配串的查找、判斷字典相應地址內容是否為空、比較字典地址相應內容是否匹配或沖突、沖突時重新生成地址、壓縮編碼輸出控制、壓縮結束控制等功能。

外接閃存數據寬度為8位,所以壓縮后輸出數據位數需要轉換。數據轉換模塊就是實現壓縮后數據由13位向8位的轉換。

時鐘處理與控制模塊主要完成時鐘的匹配與控制,對各個功能模塊分配時鐘,并初始化各使能端信號。

評論