基于Microblaze軟核的嵌入式系統設計

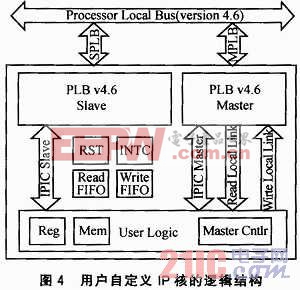

②定制用戶自己的IP核。由于嵌入式系統開發的特殊性,有時可能很難找到一款ASIC控制器,具備系統要求的所有外設接口。在這種情況下,要么用軟件實現所缺的外設功能,從而犧牲了系統性能;要么單獨購置一片該接口芯片,從而增大了電路板面積和成本。而基于FPGA軟核的設計則不存在這種問題。在XPS中定制用戶IP核與一般用VHDL編寫邏輯電路不同的是,這種定制IP可以掛接在PLB總線上,從而實現與Microblaze的通信。XPS提供自定義IP核的生成向導,圖4給出了用戶自定義IP核的邏輯結構。從圖可以看出,生成向導創建了兩個模塊,一個是與PLB總線進行交互的接口模塊IPIF,另一個是用戶邏輯模塊User_Logic。IPIF完成PLB總線信號的捕捉和協議轉換,這部分內容不需要用戶參與,用戶只需根據自定義邏輯的輸入/輸出信號在IPIF中給出相應的聲明即可;User_Logic模塊則是需要用戶進行手動添加自定義邏輯代碼的地方,在這里用戶只需關注自己需要實現的功能,不用擔心它們與Microblaze之間的通信鏈接。本文引用地址:http://www.104case.com/article/150858.htm

2.2 軟件平臺的開發

EDK的另一個組件SDK是對于XPS集成開發環境的補充,提供了一個軟件工程項目的開發環境,具有以下功能和特點:

◆基于Eclipse開源代碼標準;

◆項目管理;

◆功能完善的C/C++代碼編輯和編譯環境;

◆程序創建配置和自動化的Makefile生成;

◆完美集成的對嵌入式對象的無縫調試環境。

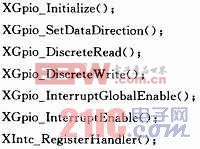

除了提供軟件的開發環境外,Xilinx公司還提供了各種IP核的API控制函數,這些API被安放在..\EDK\SW\XilinxProcessorIPLib\drivers目錄下,其中..\表示Xilinx軟件的安裝目錄。通過閱讀IP核的PDF說明文檔和API函數的C代碼,用戶可以很容易地實現對IP核的控制。以通用輸入/輸出端口GPIO為例,在文件夾..\EDK\sw\XilinxProcessorIPLib\drivers\gpio_v2_13_a下存放著與GPIO軟件編程有關的所有內容,其src子目錄下包含各種API函數的C源碼,doc目錄下包含對各種API函數的使用說明,而examples目錄下還有針對GPIO進行編程的實例源碼。一般對GPIO的操作過程為:

即首先對GPIO口進行初始化,然后設置其方向為輸入或是輸出,接下來就可以對GPIO進行讀寫。如果該GPIO可以產生中斷,則必須置位其中斷使能位,然后將中斷處理函數掛接到中斷控制器或直接掛到Microblaze的中斷位上。

評論