基于Microblaze軟核的嵌入式系統設計

摘要:結合實際項目的開發經驗,詳細講解了基于Xilinx Microblaze軟核開發的整個流程,包括硬件平臺搭建、軟件平臺開發、嵌入式操作系統的加載以及用非易失性存儲設備對FPGA進行上電配置等內容。利用FPGA軟核進行嵌入式系統開發,將得到越來越多的關注和應用。

關鍵詞:嵌入式系統;軟核;片上可編程系統;可編程邏輯門陣列

引言

近十年來,FPGA行業獲得了突飛猛進的發展,其在系統開發工作中的地位已從簡單的膠合邏輯上升到了數字系統的核心處理器件。可編程片上系統SOPC(Systern On Programmable Chip)將CPU核與外設核以及系統軟件集成到單一芯片中,幫助用戶快速“量身定制”所需要的產品,創造性地為用戶提供了基于FPGA的嵌入式設計方案。

Xilinx公司作為FPGA嵌入式軟核解決方案商,在其所有系列的FPGA中提供了Microblaze 32位軟核處理器,并推出了用于嵌入式系統編程的EDK(Embedded Development Kit)集成開發解決方案。本文結合實際項目的開發經驗,詳細講解了基于Microblaze軟核開發的整個流程,包括硬件平臺開發、軟件平臺開發、嵌入式操作系統的加載以及用非易失性存儲設備對FPGA進行上電配置等內容。

1 Microblaze的體系結構

Microblaze處理器采用RISC架構和哈佛結構,在時鐘頻率為150 MHz的情況下可以達到125 DMIPS的性能,該處理器(版本7.30)具有以下一些特征:

①32個32位通用寄存器和最多18個專用寄存器;

②32位指令系統,支持3個操作數和2種尋址方式;

③分離的32位指令和數據總線;

④通過本地存儲器總線LMB直接訪問片內的塊存儲器BRAM;

⑤具有高速的指令和數據緩存Cache,5級流水線結構;

⑥自帶硬件調試模塊MIDM;

⑦帶有8個主/從快速單工鏈路接口。

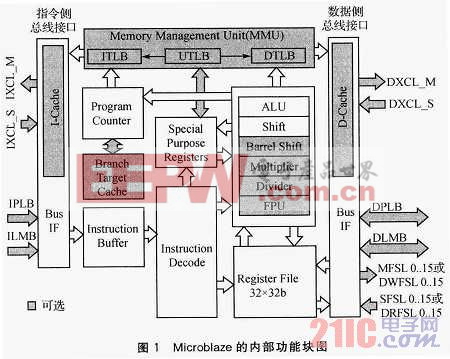

圖1給出了Microblaze的內部功能塊圖。

從圖1可以看出,Microblaze軟核與其他專用集成芯片的硬CPU核在結構上沒有大的差別,但它卻可以通過PLB總線(Processor Local Bus )與EDK軟件包將自帶的各種軟外設進行按需連接,并且支持用戶自定義IP通過PLB總線(Microblaze從7.30版本開始取消了原有的OPB總線)和FSL(Fast Simple Link)總線與Microblaze軟核連接,從而最大限度地發揮FPGA設計的靈活性。

評論